AN 1003: Multi Memory IP System Resource Planning: for Agilex™ 7 M-Series FPGAs

Visible to Intel only — GUID: irp1696537192288

Ixiasoft

Visible to Intel only — GUID: irp1696537192288

Ixiasoft

4.11. QoS Priority

You can use the QoS priority feature to improve the throughput of initiators, at the expense of other traffic. Refer to Quality of Service (QoS) Support in the Intel Agilex 7 M-Series FPGA Network-on-Chip (NoC) User Guide for details on this feature.

You can use the QoS priority feature to prioritize important connections, or balance traffic in scenarios where the NoC architecture could potentially limit the throughput of a connection due to effects like bandwidth sharing.

An important consideration when using this feature is that other traffic on the same portions of the link are also accelerated in the NoC. Therefore, assigning priority does not only accelerate the transactions that have a higher assigned priority. When a higher priority packet enters a queue at a switch, that entire queue is prioritized.

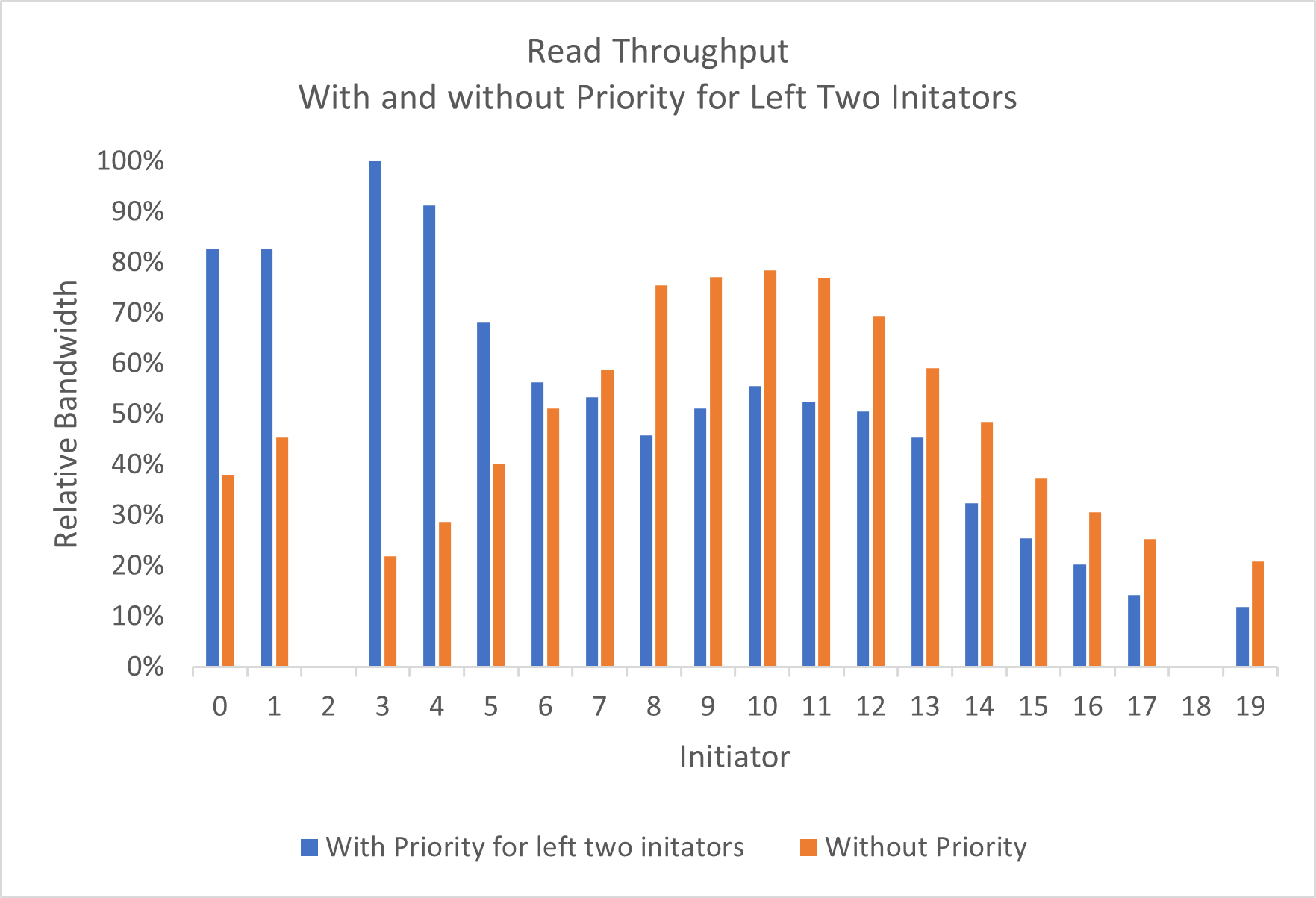

The following figure shows an example scenario in which QoS priority improves performance.

The green and yellow initiators connect to memory interfaces on the opposite side. These connections must cross a 16x16 HBM crossbar (highlighted in red).

The graph in Read Throughput With and Without Priority for Left Two Initiators illustrates the impact of applying a priority level of 3 to the leftmost two initiators, while keeping all other initiators at a priority of zero.

The prioritized initiators significantly increase their throughput, but so do the initiators on the left side of the crossbar, which disproportionately move traffic in the same direction as the prioritized initiators. This increase occurs at the expense of a decrease of other traffic that shares the NoC.