Visible to Intel only — GUID: cfr1697648343987

Ixiasoft

Visible to Intel only — GUID: cfr1697648343987

Ixiasoft

6.3.1. Measuring Performance with the Signal Tap Logic Analyzer

To conserve resources that Signal Tap uses, there is no need to probe the AXI RDATA nor WDATA signals to measure performance. Although probing all other AXI signals is not strictly required, probing most of the other AXI signals is useful for inferring information about the transactions sent.

Measuring NoC Throughput

When measuring NoC throughput, observe that the data transfer on an AXI interface occurs only when the corresponding READY and VALID signals are both asserted. You can then measure the read throughput by monitoring the number of cycles during which both RVALID and RREADY are asserted over a period of time. For write throughput, measure the number of cycles during which both WVALID and WREADY are asserted.

The following formula calculates the NoC throughput in megabytes per second:

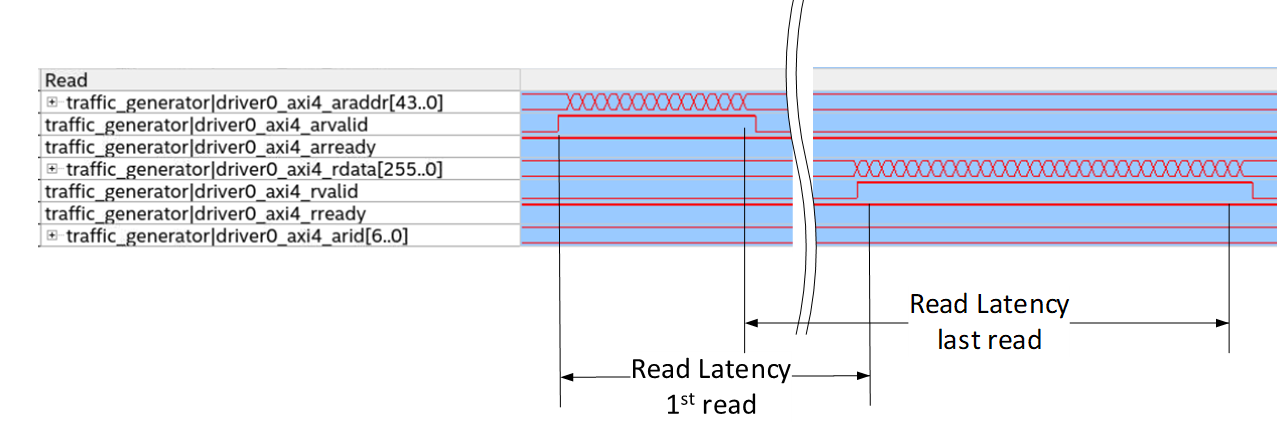

Measuring NoC Latency

You can measure NoC latency by monitoring the duration between the command being issued and the read data returning, or the write response returning. For read latency, measure the number of cycles between ARVALID and RVALID. For multicycle transactions, measure to the completion of the read data. The completion of read data occurs when both RVALID and RLAST are asserted. For write latency, measure the duration from AWVALID to BVALID. You cannot directly measure write latency. BVALID is only a proxy that is always longer than the delay for the write transaction to reach the memory controller.

In Measuring Throughput in Signal Tap, over a 50 cycle window, WVALID and WREADY are asserted for 43 cycles, resulting in a bus utilization of 86%, or 13.8 GBps, based on a 32 byte interface and a 500MHz clock.

The delay between the VALID and READY signals can also be informative. Any delay between AxVALID and AxREADY represents backpressure from the initiator. This backpressure can be caused by controller efficiency, the access pattern of your transactions, or by congestion on the NoC. Any delay between RVALID and RREADY or BVALID and BREADY is caused backpressure in your logic. Eliminate this backpressure if possible.

The AXI transactions are pipelined, and many transactions can issue before the first response returns. Therefore, to measure latency correctly, you must implement a mechanism to determine which response corresponds to each request. The easiest method is to begin measuring at the first transaction, and match requests to responses by following the sequential order of responses for each AxID. There is no general method of measuring latency from a Signal Tap capture in the middle of an ongoing set of transactions. To match transactions requests to their responses, you must use the application-specific identifying characteristics, such as observing what data transfers.