Visible to Intel only — GUID: lhj1696538150380

Ixiasoft

1. Answers to Top FAQs

2. About This Application Note

3. Component Bandwidth Projections and Limitations

4. Resource Planning for Intel Agilex® 7 M-Series FPGAs

5. Factors Affecting NoC Performance

6. Debugging the NoC

7. Document Revision History of AN 1003: Multi Memory IP System Resource Planning for Intel Agilex® 7 M-Series FPGAs

4.1. Hard Memory NoC Resource Planning Overview

4.2. I/O Bank Blockage

4.3. Planning Avalon® Streaming Utilization

4.4. Planning for Initiator Blockage Impact from GPIO, LVDS SERDES, and PHY Lite Bypass Mode

4.5. Planning NoC PLL and I/O PLL

4.6. Pin Planning for HPS EMIF

4.7. Planning for an External Memory Interface

4.8. Planning for HBM2E

4.9. Planning for the Fabric NoC

4.10. Planning for AXI4-Lite

4.11. Planning NoC and Memory Solution Clocks

5.1. Recommended Performance Tuning Procedure

5.2. NoC Initiator and Target Clock Rate

5.3. Recommended NoC Design Topologies

5.4. Traffic Access Pattern and Memory Controller Efficiency

5.5. Traffic Access Pattern Due To Multiple Traffic Flows

5.6. Transaction Size

5.7. Congestion Interaction

5.8. Bandwidth Sharing At Each Switch

5.9. Exceeding NoC Bandwidth Limits

5.10. Maximum Number of Outstanding Transactions

5.11. QoS Priority

5.12. AxID

5.13. Example: 2x2 HBM Crossbars

5.14. Example: 16x16 Crossbar

Visible to Intel only — GUID: lhj1696538150380

Ixiasoft

5.12. AxID

The NoC bridges and the EMIF and HBM2E memory controllers can all take advantage of AxID ordering rules to return data out of order, and return certain transactions earlier.

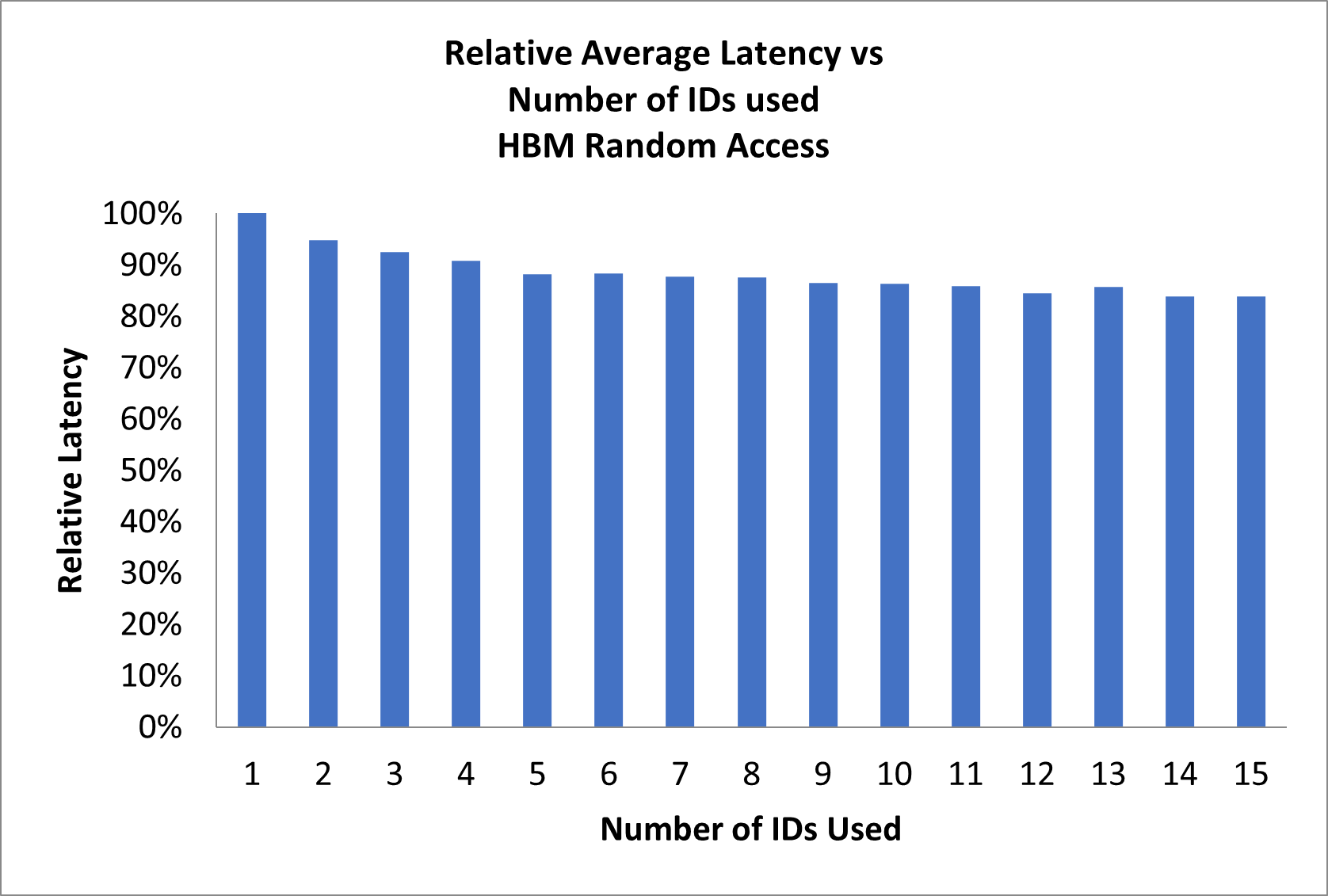

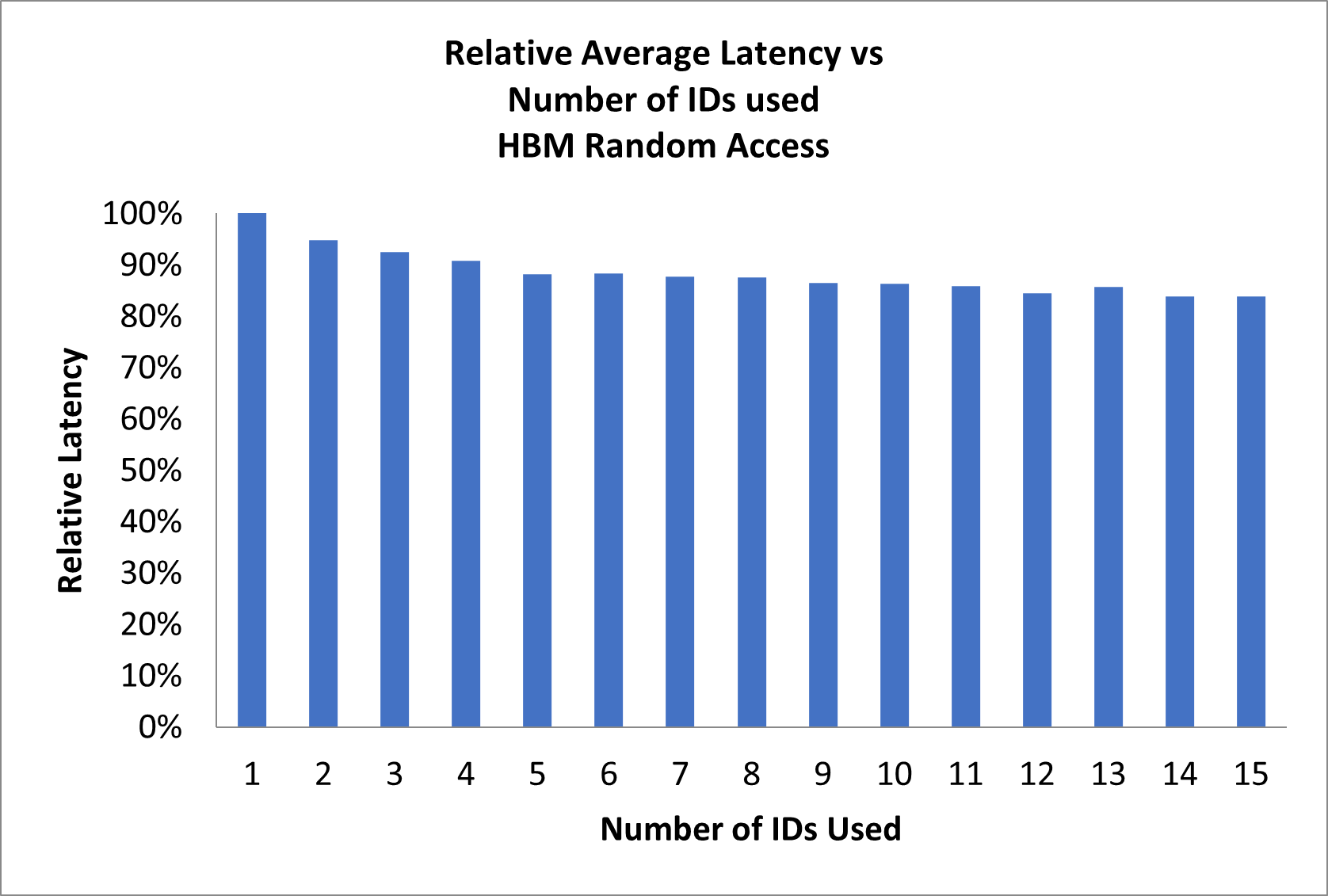

Using different AxID for transactions that do not need to be returned in order can reduce average latency, especially in non-sequential access patterns.

A typical application of this technique is for a multiport front end or other traffic combiner in front of the NoC initiator. If those traffic sources are independent, they should use different AxIDs. The NoC bridges and memory controllers support up to 16 unique AxIDs.

Figure 37. Relative Average Latency Versus Number of IDs Used HBM Random Access