Visible to Intel only — GUID: oln1694015416580

Ixiasoft

Visible to Intel only — GUID: oln1694015416580

Ixiasoft

4.8. Planning for HBM2E

At maximum performance, HBM2E can provide up to 410GBps per stack. Combining the two HBM2E stacks can provide up to 820 GBps of peak memory bandwidth.

To achieve the optimum possible bandwidth on HBM2E:

- You must use all 16 initiators.

- Place all 16 initiators in the center.

- Place 9 initiators directly across from the UIB.

- Place the remaining initiators in adjacent sectors on the left and right of the UIB section to create a balanced distribution of initiators. The actual physical placement of these seven remaining initiators also depends on your system requirements of GPIO, EMIF, and HPS EMIF.

Initial performance analysis does not show bandwidth impact when placing the HBM2E initiator where the traffic goes through multiple switches in the horizontal NoC to communicate with targets. You could see latency impact in your specific application.

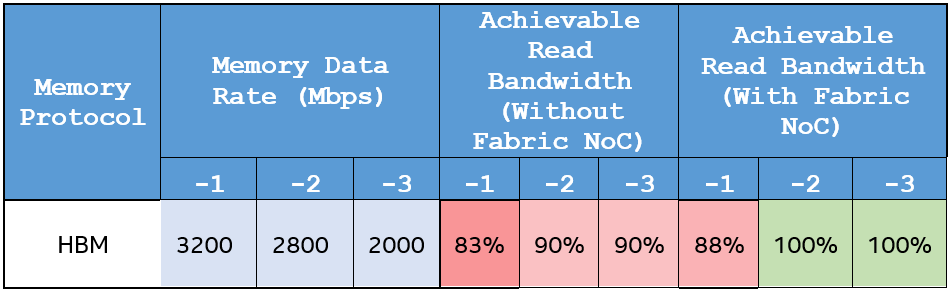

HBM2E also has a limitation on achievable bandwidth across speed grade, even if HBM2E is running faster. This impact occurs regardless of the hard memory controller capabilities. Achievable Bandwidth for HBM2E Across Device Speed Grade uses color coding to represent the effect of initiator frequency on bandwidth loss. Green color shading signifies no degradation, while red color shading indicates the severity of bandwidth loss. More than 16 initiators are needed to fully saturate a -1 device bandwidth due to limited initiator frequency support.

If your application requires less bandwidth, you can choose to use fewer initiators with centralized placement, talking to multiple targets.