Visible to Intel only — GUID: pkk1501796697014

Ixiasoft

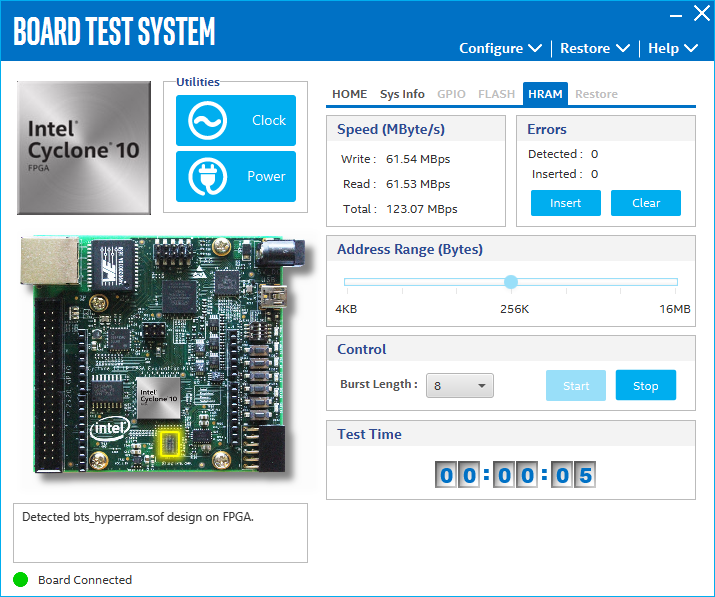

6.5. The HyperRAM Tab

The HyperRAM tab allows you to test the HyperRAM by reading and writing to a selected number of addresses with selectable burst length. The supported burst lengths are 2, 4, 8, 16, 32, 64, and 128.

Figure 21. The HyperRAM Tab

| Control | Description |

|---|---|

| Speed (MByte/s) |

|

| Errors | These controls display data errors detected during analysis and allow you to insert errors.

|

| Address Range (Bytes) | Determines the number of addresses to use in each iteration of reads and writes. |

| Test Times | This item displays test times since you last clicked Start. |

| Control |

|