Visible to Intel only — GUID: lxp1501796826449

Ixiasoft

6.7. The Clock Control

The Intel® Cyclone® 10 LP FPGA Evaluation Kit Clock Control application sets the programmable oscillator to any frequency between 3 KHz and 200 MHz.

The Clock Control communicates with the Intel® MAX® 10 device on the board through the JTAG bus. The programmable oscillator is connected to the Intel® MAX® 10 device through a 2-wire serial bus.

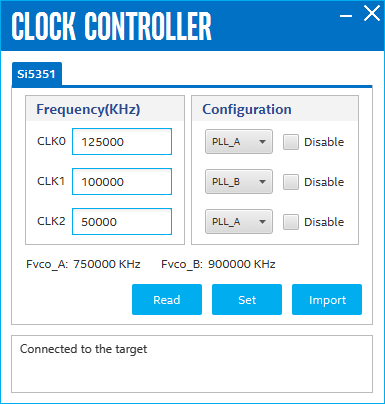

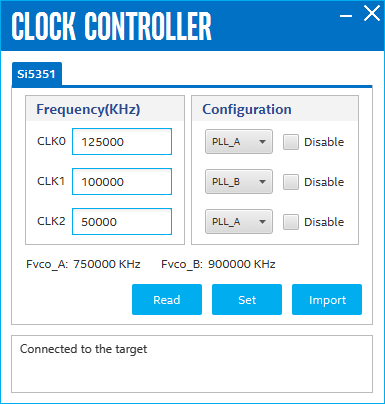

Figure 23. The Si5351 Tab

| Control | Description |

|---|---|

| Fvco_A/Fvco_B | Displays the generating signal value of the voltage-controlled oscillator. |

| Frequency (KHz) | Allows you to specify the frequency of the clock. |

| PLL Choose | Allows you to specify the PLL used by the clock. |

| Disable | Disable each clock output as required. |

| Read | Reads the current frequency setting for the oscillator associated with the active tab. |

| Set | Sets the programmable oscillator frequency for the selected clock to the value in the CLK0 to CLK2 controls. Frequency changes might take several milliseconds to take effect. You might see glitches on the clock during this time. Intel recommends resetting the FPGA logic after changing frequencies. |

| Import | Allows you to import a register table file generated by Clock Builder. You can reset the clock to default by importing the default register file "Si5351A-Registers.txt" in the application folder. |