Visible to Intel only — GUID: mvq1520633313085

Ixiasoft

Visible to Intel only — GUID: mvq1520633313085

Ixiasoft

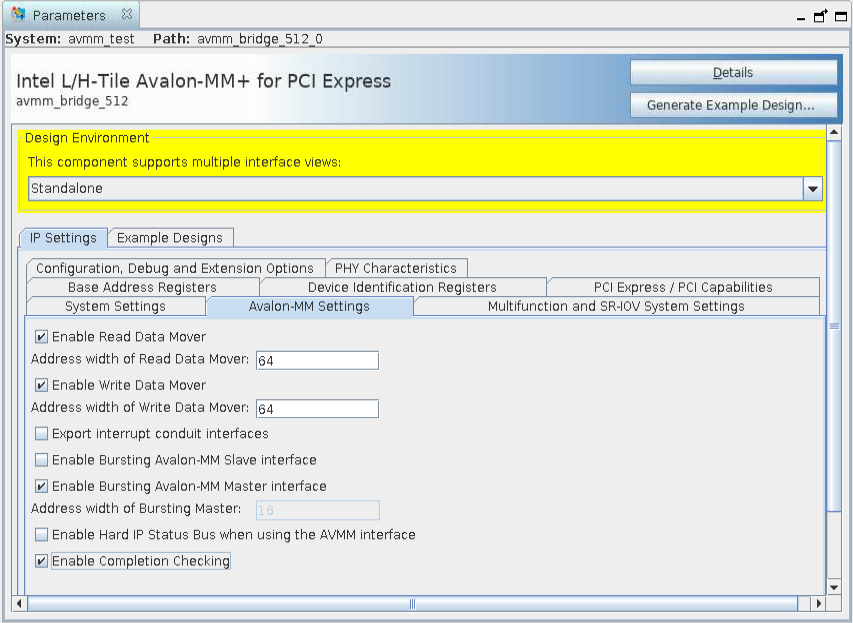

4.1. Avalon-MM Settings

| Parameter | Value | Default | Description |

|---|---|---|---|

| Enable Read Data Mover | On/Off | On | When On, the IP core includes the Read Data Mover. |

| Address width of Read Data Mover | 10 - 64 bits | 64 bits | Specifies the address width for the Read Data Mover. |

| Enable Write Data Mover | On/Off | On | When On, the IP core includes the Write Data Mover. |

| Address width of Write Data Mover | 10 - 64 bits | 64 bits | Specifies the address width for the Write Data Mover. |

| Export interrupt conduit interfaces | On/Off | Off | When On, the IP core exports internal interrupt signals to the top-level RTL module. The exported signals support legacy interrupts. |

| Enable bursting Avalon-MM Slave interface | On/Off | Off | When On, the high performance Avalon-MM Slave interface is enabled. This interface is appropriate for high bandwidth applications such as transferring blocks of data. The maximum burst count supported is 8. |

| Address width of bursting Slave | 10 - 64 bits | 64 bits | Specifies the address width for the high performance Avalon-MM Slave interface. This parameter is accessible only after the high performance bursting Avalon-MM Slave interface is enabled. |

| Enable bursting Avalon-MM Master interface | On/Off | On | When On, the high performance Avalon-MM Master interface is enabled. This interface is appropriate for high bandwidth applications such as transferring blocks of data. The maximum burst count supported is 8. |

| Enable hard IP status bus when using the Avalon-MM interface | On/Off | Off | When you turn this option On, your top-level variant includes signals that are useful for debugging, including link training and status, and error signals. The following signals are included in the top-level variant:

|

| Enable Completion Checking | On/Off | Off | With this option On, when the Read Data Mover in the IP core issues an upstream Read to the host and the host does not return a completion after a time period exceeding the completion timeout value specified in a PCIe Hard IP Configuration register, the output rddm_tx_data_o[15] is asserted to indicate a completion timeout error. No associated data is returned to the Read Data Mover for the descriptor that corresponds to the completion timeout error. If an external Avalon® -MM Master issues a Read request to the BAS interface (which the BAS interface then forwards to the host), and a completion timeout happens, the BAS interface will respond to the Avalon® -MM Master with dummy data and set the outputs bas_response_o[1:0] to 2'b10 to indicate an unsuccessful completion.

The possible encodings for bas_response_o[1:0] are:

|