Visible to Intel only — GUID: jbq1680011805850

Ixiasoft

3.5.2.5.1. Build and Install Netdev Driver

3.5.2.5.2. Enable VFs if SRIOV is Supported

3.5.2.5.3. Configure the Number of Channels Supported on the Device

3.5.2.5.4. Configure the MTU Value

3.5.2.5.5. Configure the Device Communication

3.5.2.5.6. Configure Transmit Queue Selection Mechanism

3.5.2.5.7. Test Procedure by Using Name Space Environment

3.5.2.5.8. PIO Test

Visible to Intel only — GUID: jbq1680011805850

Ixiasoft

3.5.2.4.5.3. Testing Bitstream Configuration beyond 256 Channels (for DPDK Poll Mode Driver)

Note: In case, if the *.sof file generated with the number of channels > 256, please follow this procedure.

- Define following macros in dpdk/drivers/net/mcdma/rte_pmd_mcdma.h

#define IFC_MCDMA_DIDF

- Configure the mem zone in dpdk-stable/config/rte_config.h

#define RTE_MAX_MEMZONE 20480

In case of AVMM, BDF is provided as an argument and you must define examples/mcdma-test/perfq/meson.build

-DIFC_MCDMA_SINGLE_FUNC

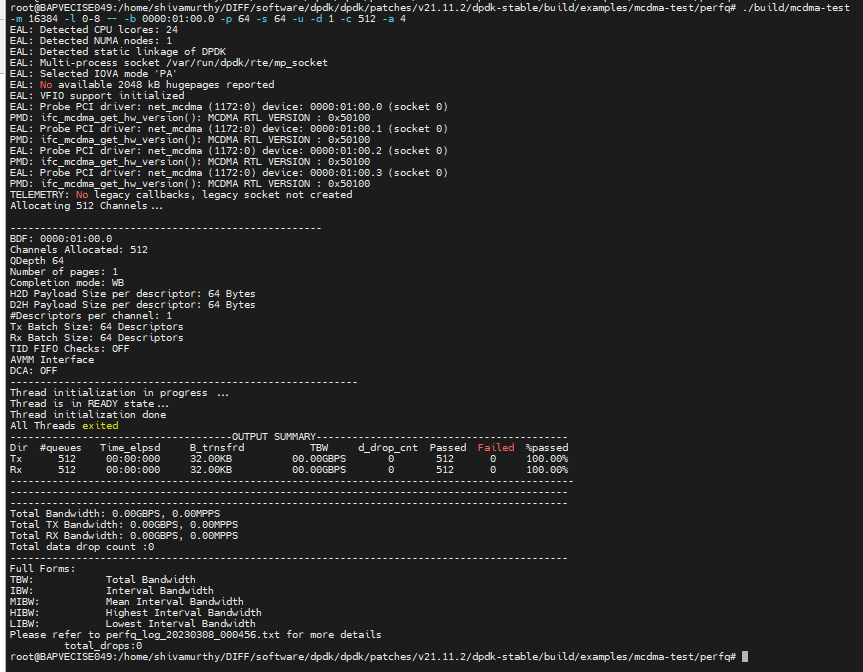

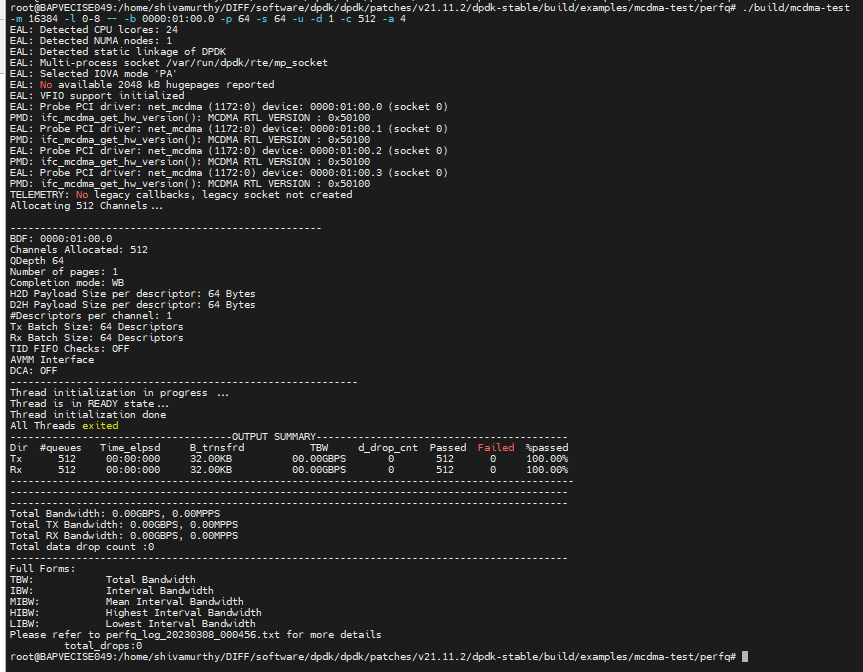

Figure 39. Example Command Output For AVMM

Configuration for AVST/AXIST LB and AVST/AXIST pktgen Undefined single function mode in examples/mcdma-test/perfq/meson.build

-UIFC_MCDMA_SINGLE_FUNC

Note: bdf is not provided to run the test

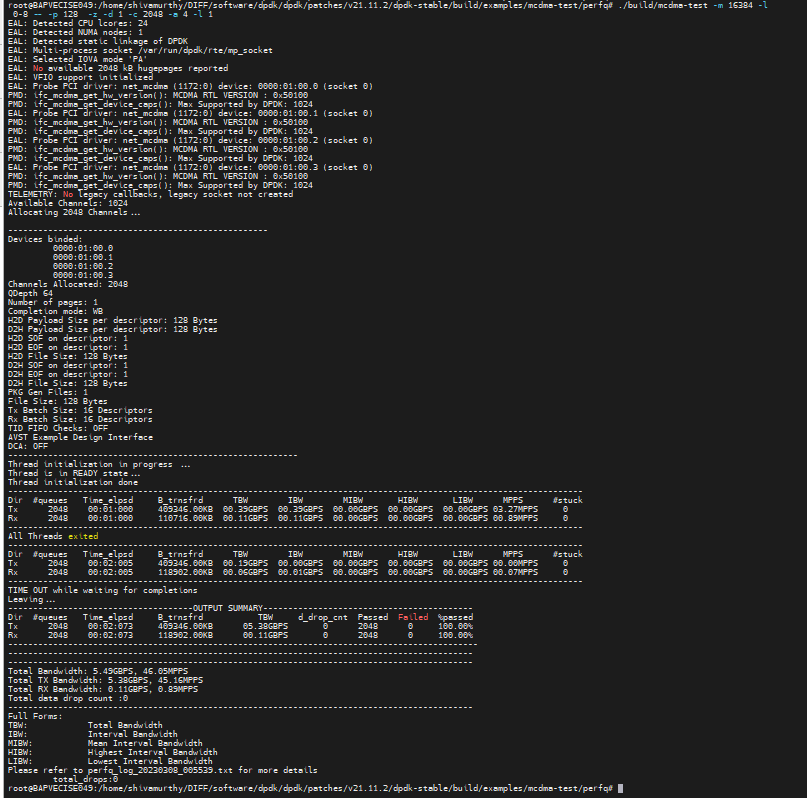

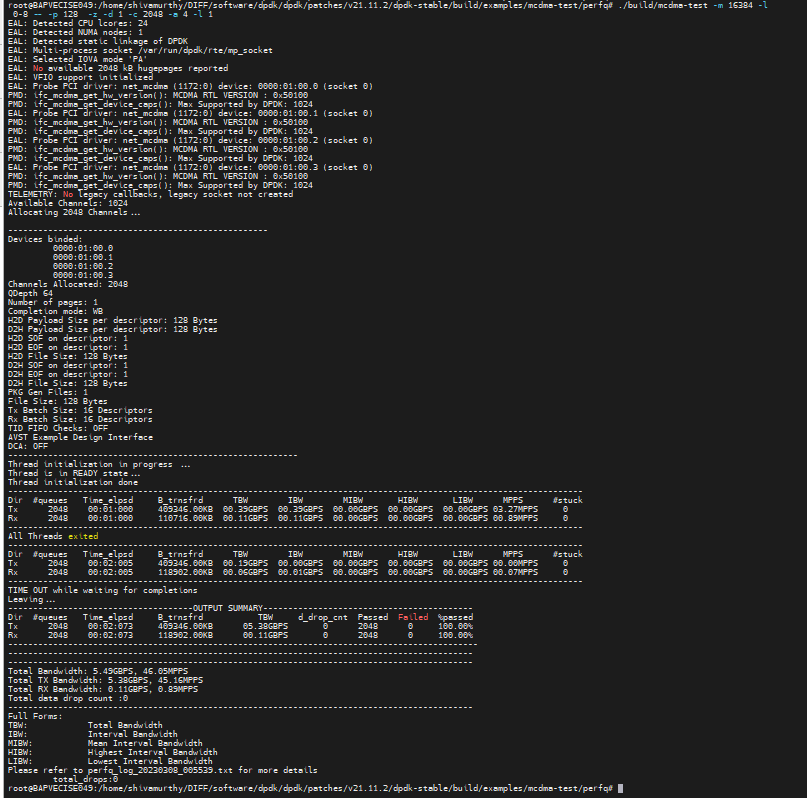

Figure 40. Example Command Output for AVST/AXIST

Command for pktgen: :

./build/mcdma-test –m 16384 –l 0-8 - -b -p 64 -l 1 -z -d 1 -c 2048 -a 4

Command for loopback:

./build/mcdma-test –m 16384 –l 0-8 - -b -p 64 -l 2 -i -d 1 -c 2048 -a

Note: In the current release, single page is supported in DIDF mode.

Note: In the current release, simultaneous process is not supported in DIDF mode. You can run one process with 2K channels.