Visible to Intel only — GUID: xwx1596241385782

Ixiasoft

3.5.2.5.1. Build and Install Netdev Driver

3.5.2.5.2. Enable VFs if SRIOV is Supported

3.5.2.5.3. Configure the Number of Channels Supported on the Device

3.5.2.5.4. Configure the MTU Value

3.5.2.5.5. Configure the Device Communication

3.5.2.5.6. Configure Transmit Queue Selection Mechanism

3.5.2.5.7. Test Procedure by Using Name Space Environment

3.5.2.5.8. PIO Test

Visible to Intel only — GUID: xwx1596241385782

Ixiasoft

2.6.2. Hardware Test Results

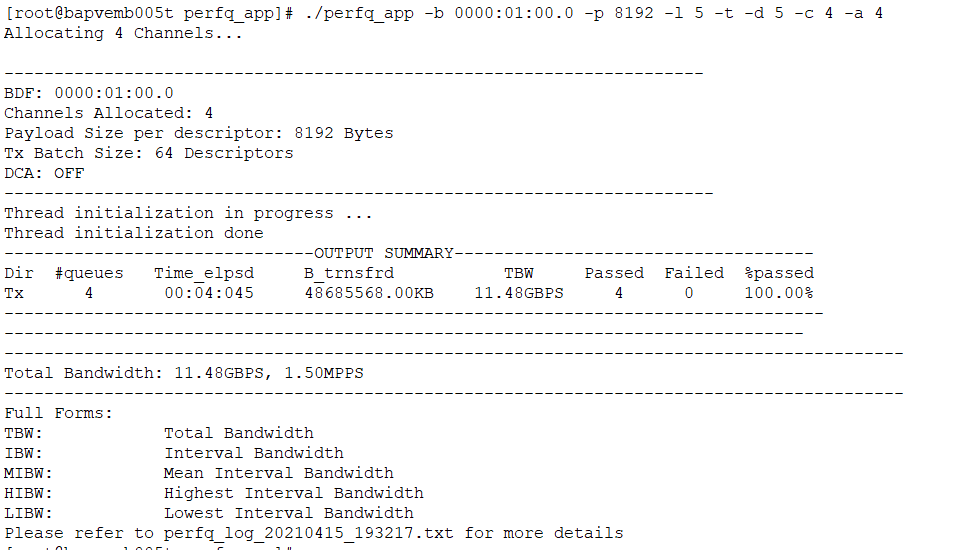

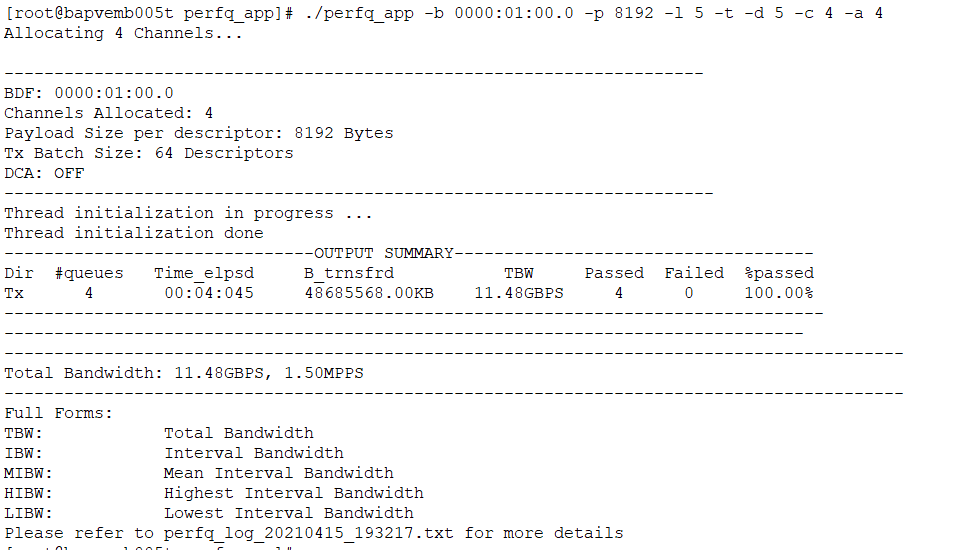

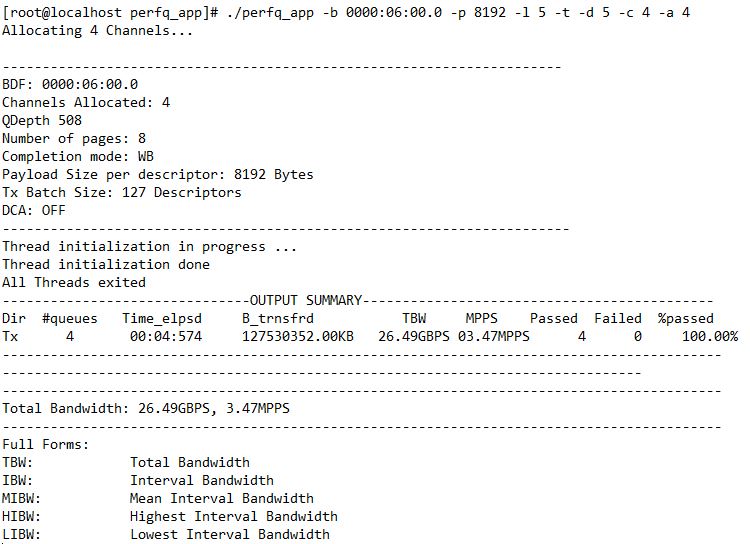

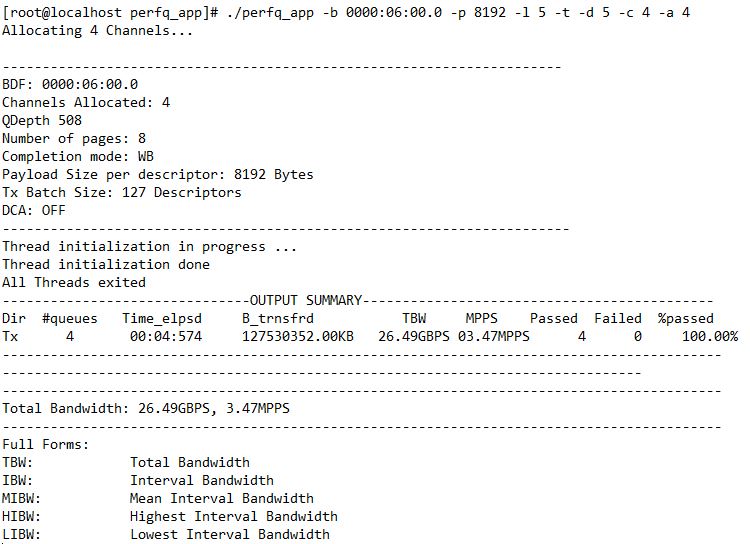

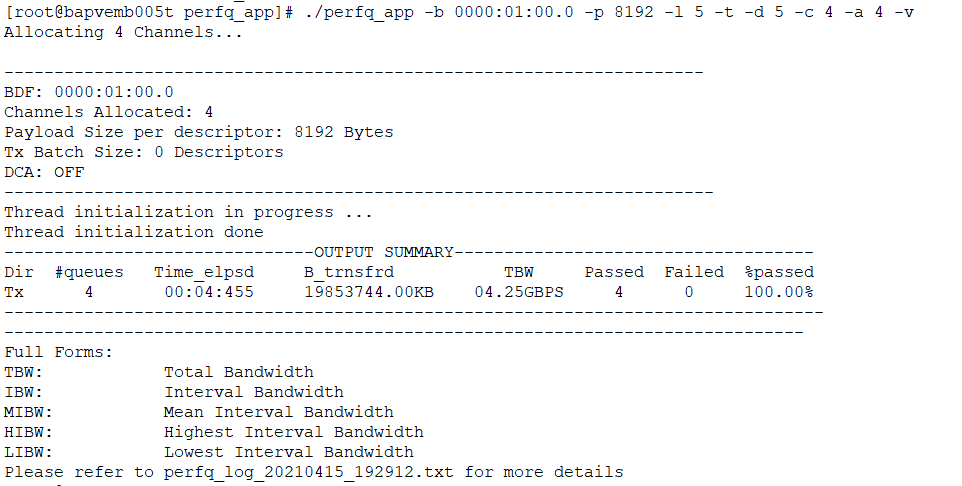

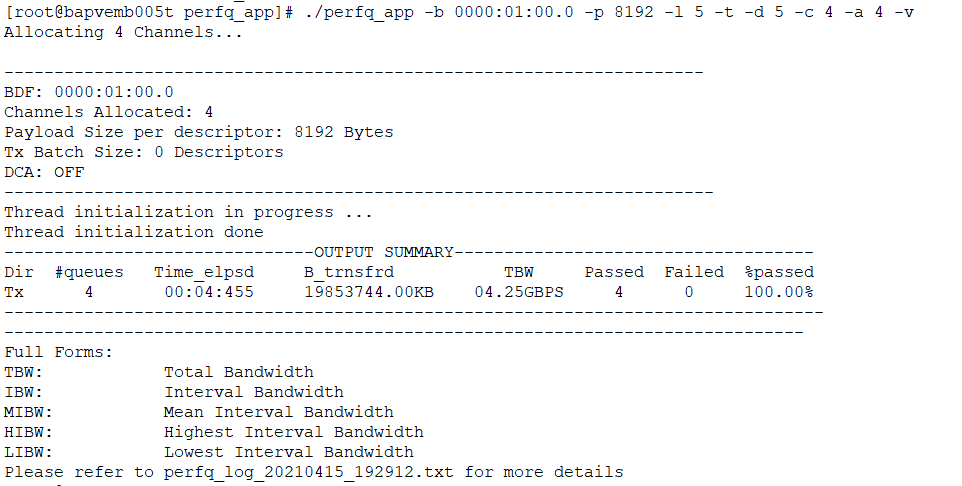

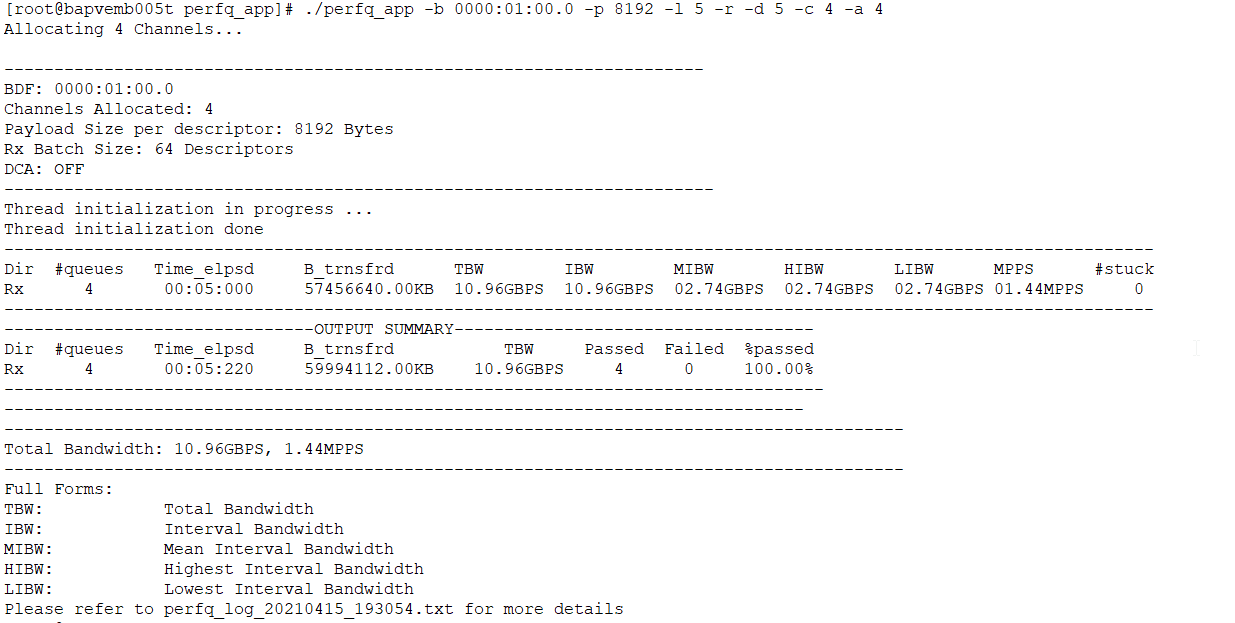

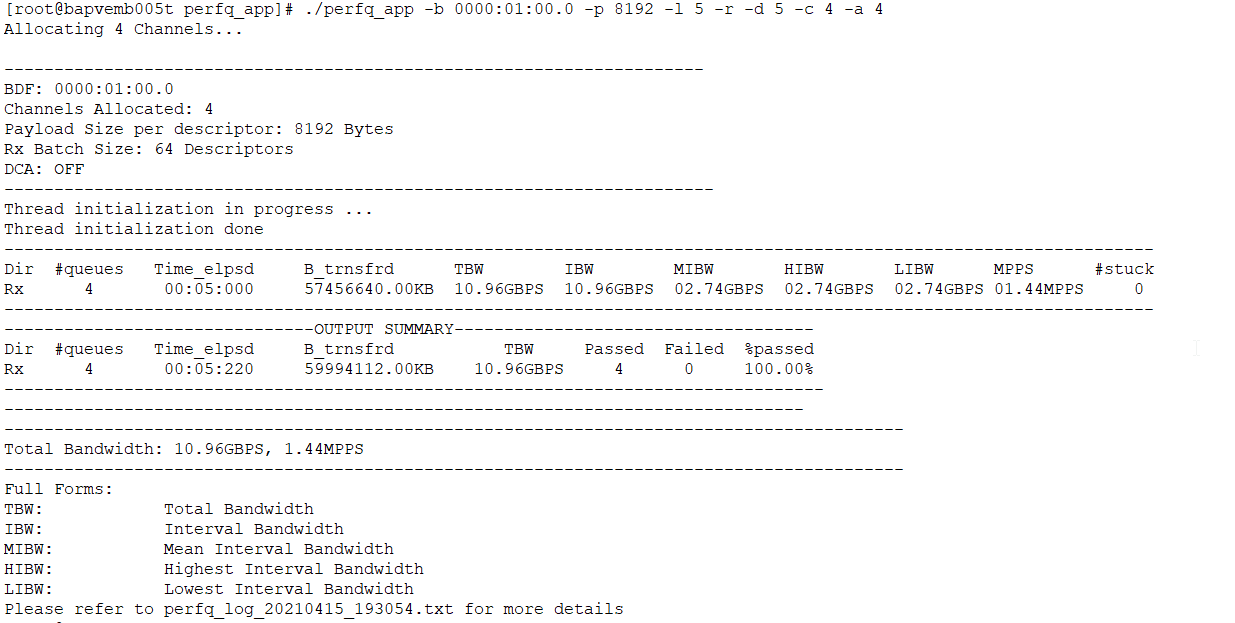

The Custom Driver was used to generate the following output:

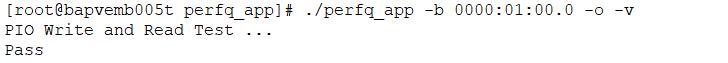

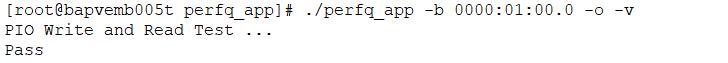

Figure 15. PIO Test-o option

Figure 16. H2D Avalon-MM Write-t option. Note: This hardware test was run with the Stratix® 10 GX H-tile PCIe Gen3 x16 configuration.

Figure 17. H2D Avalon-MM Write Agilex™ 7 F-Series P-Tile PCIe Gen4 x16 The following hardware test was run with Agilex™ 7 F-Series P-Tile PCIe Gen4 x16 configuration using Custom Driver.

Figure 18. H2D Avalon-MM Write with Data Validation Enabled-t -v option. Note: This hardware test was run with the Stratix® 10 GX H-tile PCIe Gen3 x16 configuration.

To enable data validation using -v option, set the software flags in user/common/mk/common.mk as follows:

cflags += -UPERFQ_PERF cflags += -DPERFQ_LOAD_DATA

Note: Hardware test with P-Tile Gen4 x16 may be added in a future release.

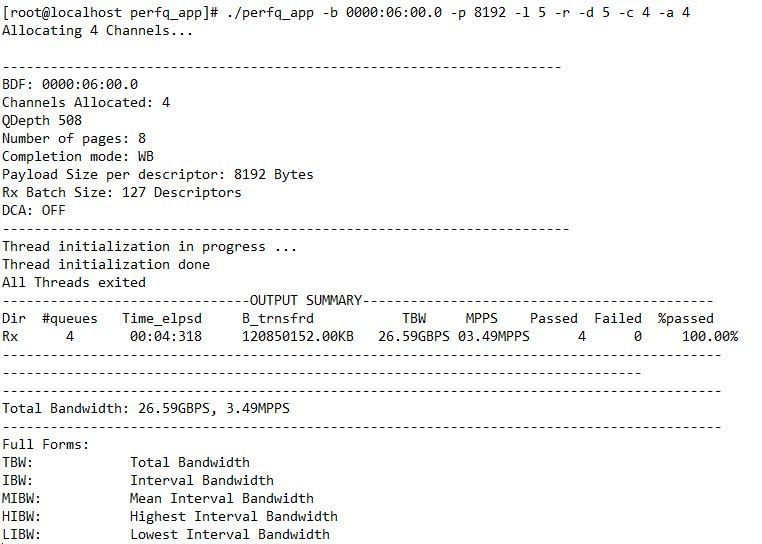

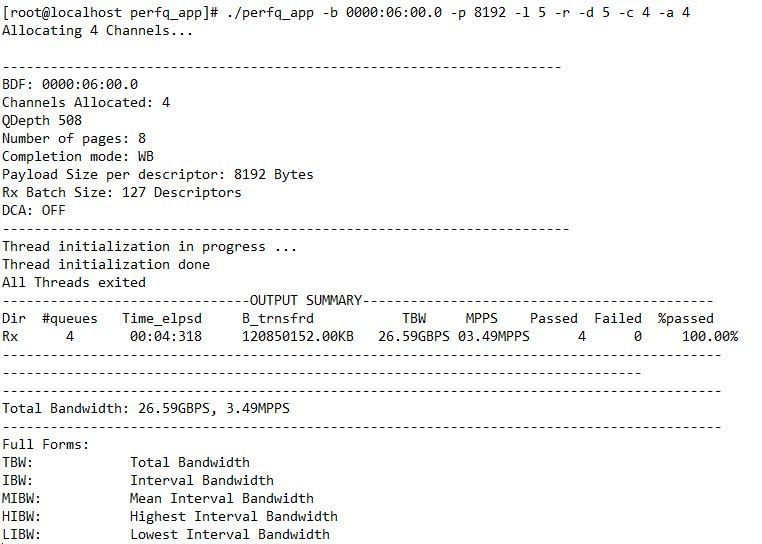

Figure 19. D2H Avalon-MM Read-r option. Note: This hardware test was run with the Stratix® 10 GX H-tile PCIe Gen3 x16 configuration.

Figure 20. D2H Avalon-MM Read Agilex™ 7 F-Series P-Tile PCIe Gen4 x16