AN 701: Scalable Low Latency Ethernet 10G MAC using Intel Arria 10 1G/10G PHY

ID

683343

Date

11/06/2017

Public

Test Scenario for Design Example with IEEE 1588v2

To perform test case, follow these steps:

- Set the start up with channel configured to 10G mode.

- Perform basic MAC configuration, PHY speed configuration, 1588 component configuration and PTP clock mode configuration for all 2 channels.

- Wait for the design example to assert the channel_ready signals for all 2 channels.

- Send the following packets:

- Non-PTP

- No VLAN, PTP over Ethernet, PTP Sync Message, 1-step PTP

- VLAN, PTPover UDP/IPv4, PTP Sync Message,1-step PTP

- Stacked VLAN, PTP over UDP/IPv6, PTP Sync Message, 2-step PTP

- No VLAN, PTP over Ethernet, PTP Delay Request Message, 1-step PTP

- VLAN, PTPover UDP/IPv4, PTP Delay Request Message, 2-step PTP

- Stacked VLAN, PTP over UDP/IPv6, PTP Delay Request Message, 1-step PTP

- Repeat steps 2 to 4 for 1G, 100M and 10M speed mode.

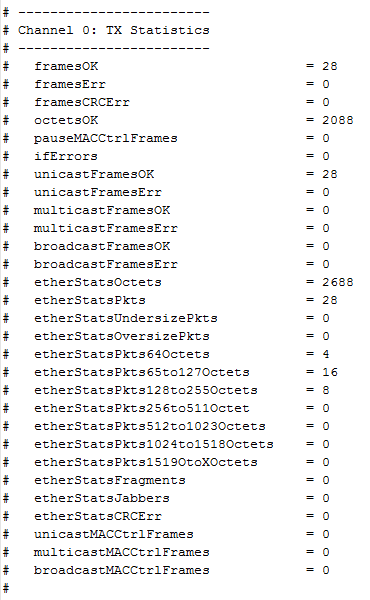

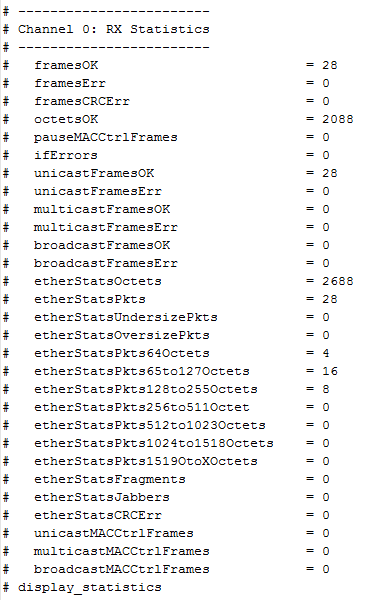

- When the simulation ends, refer to the transcript window for channel 0 MAC TX and RX statistic counter results.

Figure 5. Channel 0 MAC TX Statistic Counter

Figure 6. Channel 0 MAC RX Statistic Counter

- If channel 0 Avalon_st RX interface successfully receives all 28 packets, the transcript displays PASSED.