Visible to Intel only — GUID: csq1692201125147

Ixiasoft

Visible to Intel only — GUID: csq1692201125147

Ixiasoft

1.16.4.1. Example: Using SDC-on-RTL Features

You can work with both new and pre-existing designs that incorporate components from diverse sources, including Verilog, VHDL, IP, and Platform Designer systems. Suppose your design contains nodes that require constraint definitions, such as clocks, generated clocks, or asynchronous paths, across various hierarchy levels. In that case, you can efficiently target these nodes with SDC-on-RTL constraints. Your design must successfully pass the Analysis & Elaboration stage of the Compiler to support a seamless and effective testing process.

The following steps demonstrate the process of setting up timing constraints for your designs by targeting RTL node names:

- Enable the RTL Analysis Debug Mode Compiler option under Assignments > Settings > Compiler Settings, or by specifying the following assignment in the project .qsf:

set_global_assignment -name RTL_ANALYSIS_DEBUG_MODE ON

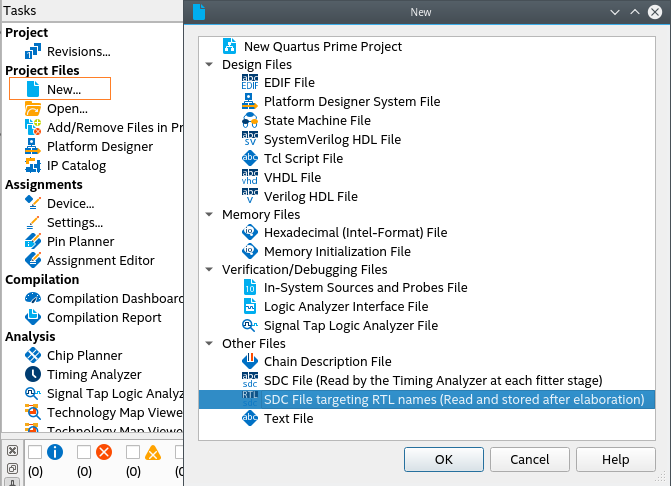

Enabling RTL Analysis Debug Mode mode during the Analysis & Elaboration makes the Elaborated, Swept, Instrumented, and Constrained checkpoints available. When this option is off (the default) only the Elaborated and Swept checkpoints are available. - Click New in the left-hand Tasks pane. The New dialog appears.

- Click SDC File targeting RTL Names (Read and stored after elaboration).

Figure 127. New Dialog Box

- Click OK.

- Within the new SDC-on-RTL file, formulate a comprehensive set of constraints targeting nodes by their RTL names. For information about how to obtain a list of the supported commands, refer to Creating Constraints in SDC-on-RTL SDC Files.

- Ensure the constraint targets are correct and the selected design passes the Analysis & Elaboration compilation stage as the constraints are read during this stage and applied to the elaborated netlist. This step is pivotal as it empowers the software to generate a database of your design. Additionally, it grants access to various checkpoints from where you can access the RTL Analyzer.

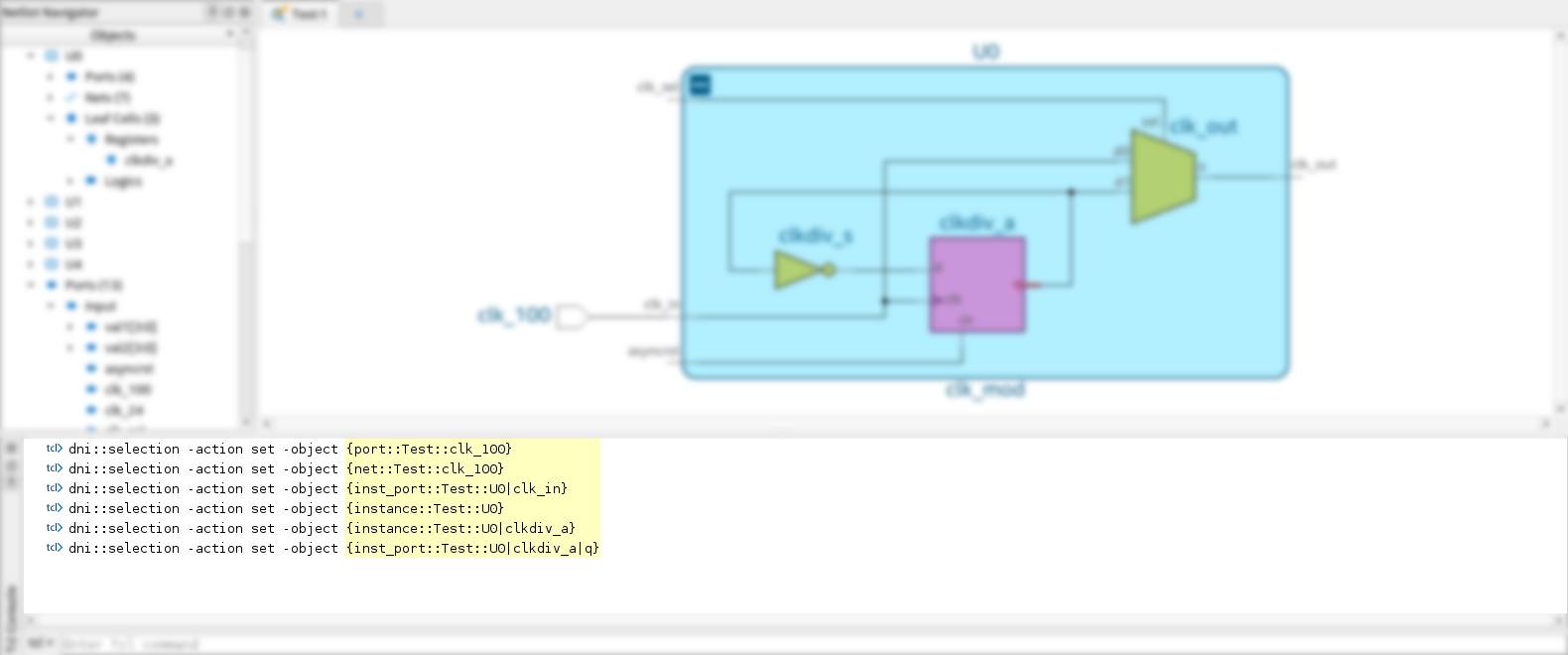

The RTL Analyzer assists you in locating specific netlist nodes within your design that require constraint application. RTL Analyzer allows you to navigate your design and select your desired target nodes. Subsequently, you can use corresponding Tcl commands generated within the Tcl console to extract hierarchical node names from the Tcl commands. You can use the Copy Hierarchy Path Name command to simplify copying hierarchy path names from the RTL Analyzer to the clipboard, as Copying Hierarchy Path Names describes. For more information about the RTL Analyzer, refer to Using the RTL Analyzer.

Figure 128. Locating Specific Netlist Nodes in the RTL Analyzer

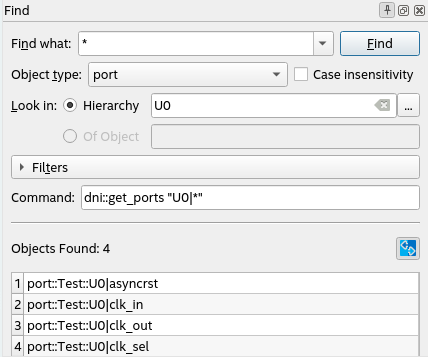

Alternatively, you can locate nodes within your target netlist using the Find tool, which is available from the Edit menu in the RTL Analyzer. The Find tool allows you to search objects within the updated database from the checkpoint accessed.

Figure 129. Find Dialog in the RTL Analyzer

In addition, you can create your collections by focusing on the inputs and outputs of your design through the use of the get_ports command. Within your design, you can locate specific nets using the get_nets command or target pins using the get_pins command.

After establishing your timing constraints in your designs, use the following examples as a guide to set up your constraints, specifically focusing on RTL node names, thereby ensuring precision and efficiency throughout your design process.