Visible to Intel only — GUID: ptv1725475212544

Ixiasoft

Visible to Intel only — GUID: ptv1725475212544

Ixiasoft

1.16.5.1. Entity-based SDC-on-RTL Constraints Example

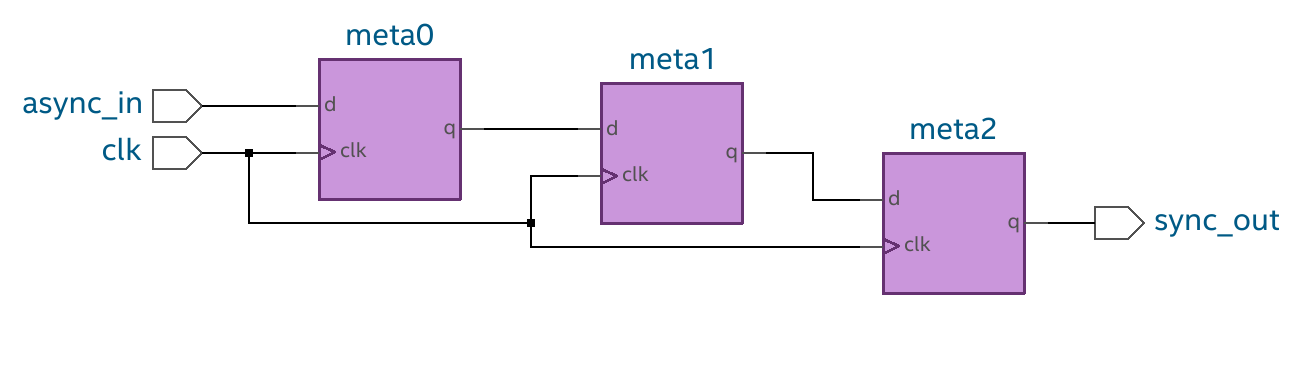

Typically, you would pair such a module with a false path exception to the first register in the chain, meta0. The false path exception might look like the following, and be placed in any of the main .sdc files for your project:

set_false_path -to *|meta0

The leading wildcard covers all possible instantiations of the module in a design. However, such a broad false path is risky, because the constraint could also unintentionally cut paths in RTL supplied by other groups or vendors. A safer method is to apply an exception to only instances of the cdc_sync module by using the following two steps:

- Define the false path exception in its own .sdc file.

- Add the .sdc file to the project with the appropriate entity-bound assignment.

The following example shows the false path exception in an .sdc file named cdc_sync_false_path.rtlsdc. The false path example cuts the path through the async_in port of the module, to demonstrate the support for SDC-on-RTL capabilities. You could also implement the same functionality with a cut to the meta0 register (-to [get_registers meta0]):

set_false_path -through [get_ports async_in]

The example does not specify a leading wildcard, because target node names in entity-bound SDC-on-RTL constraints are scoped to the module (entity) they are bound to. Write the target node names as if the module or entity was the top level of a design. When the constraints are processed, the target node names automatically include the prepended instance paths.

Add the .sdc file to the project with the following setting in the .qsf. The setting associates, or binds, the constraints and exceptions in the cdc_sync_false_path.rtlsdc file with all instances of the cdc_sync module, which you specify with the -entity option.

set_global_assignment -name RTL_SDC_FILE cdc_sync_false_path.rtlsdc -entity cdc_sync