Quartus® Prime Pro Edition User Guide: Design Compilation

ID

683236

Date

9/30/2024

Public

Visible to Intel only — GUID: vhd1725653343341

Ixiasoft

1.1. Compilation Overview

1.2. Design Analysis & Elaboration

1.3. Design Synthesis

1.4. Design Place and Route

1.5. Incremental Optimization Flow

1.6. Fast Forward Compilation Flow

1.7. Full Compilation Flow

1.8. HSSI Dual Simplex IP Generation Flow

1.9. Exporting Compilation Results

1.10. Clearing Compilation Results

1.11. Integrating Other EDA Tools

1.12. Compiler Optimization Techniques

1.13. Compilation Monitoring Mode

1.14. Viewing Quartus Database File Information

1.15. Understanding the Design Netlist Infrastructure

1.16. Using Synopsys* Design Constraint (SDC) on RTL Files

1.17. Using the Node Finder

1.18. Synthesis Language Support

1.19. Synthesis Settings Reference

1.20. Fitter Settings Reference

1.21. Design Compilation Revision History

2.1. Factors Affecting Compilation Results

2.2. Strategies to Reduce the Overall Compilation Time

2.3. Reducing Synthesis Time

2.4. Reducing Placement Time

2.5. Reducing Routing Time

2.6. Reducing Static Timing Analysis Time

2.7. Setting Process Priority

2.8. Reducing Compilation Time Revision History

Visible to Intel only — GUID: vhd1725653343341

Ixiasoft

2.3.1.2. Precompiled Component Generation Flow

Complete the following steps to use the Precompiled Component Generation flow for your project:

- Enable Precompiled Components Generation, as Enabling Precompiled Components Generation describes.

- Create a new Quartus Prime project, or open a project you have previously created.

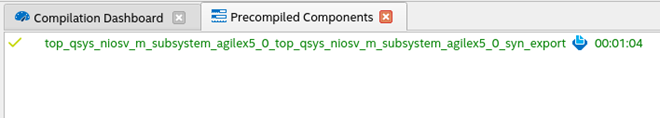

- After adding any design files to the project with Project > Add/Remove Files in Project, double-click Analysis & Elaboration on the Compilation Dashboard. Precompiled Component Generation runs as a sub-process of Analysis & Elaboration. To view the status of Precompiled Component Generation during Analysis & Elaboration, click the Progress Bar icon that appears in Compilation Dashboard.

Figure 149. Progress Bar Icon

The following applies if you have shared caches:

- For each IP in the project that is available in a shared IP cache, the Compiler skips that IP, retrieves the entry from the shared IP cache, and copies the entry to the project’s cache. A message informs you that the component is loading from the cache.

- For each IP that is not available in any of the shared IP caches, and if the shared IP caches are read-only, the Compiler partially synthesizes the IP and places the results in the project cache.

- If there are read-write shared IP caches, the Compiler writes the compiled IP to the first writable cache in the list and issues a message when complete.

- If you have different projects, using different IP variations, with the same name, accessing the same shared IP cache, the different IP variations are considered unique IPs in the shared IP cache.

- You can optionally clear the IP cache by clicking Project > Clean Project.

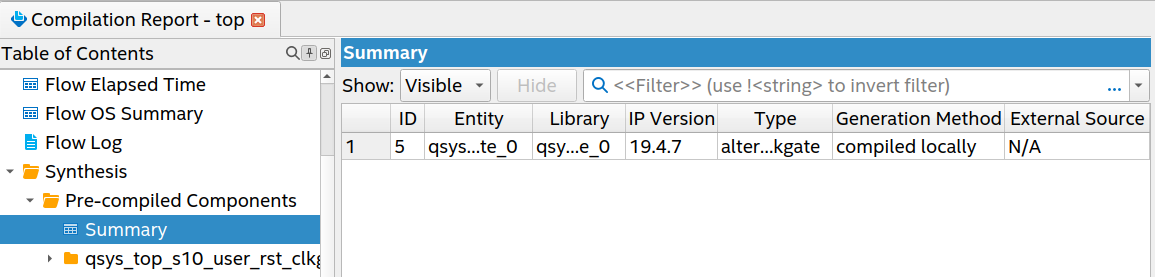

- Following Precompiled Component Generation, you can view reports on each precompiled component under the Synthesis > Pre-compiled Components report folder.

Figure 150. Pre-compiled Components Report Folder

- Continue with the compilation of your design by running Analysis & Synthesis and full compilation when ready.