Visible to Intel only — GUID: lzi1692369795357

Ixiasoft

Visible to Intel only — GUID: lzi1692369795357

Ixiasoft

1.2. Design Analysis & Elaboration

The Analysis & Elaboration stage comprises a series of checkpoints. You can preview your design results at each checkpoint as shown in Analysis & Elaboration Checkpoints, where:

- Elaborated: Provides an unmodified preview of your design captured directly from RTL.

- Instrumented: Provides an instrumented preview with system-level debugging (debug fabric and Signal Tap logic analyzer inserted in your design). This checkpoint is disabled by default (Hint: See Note below to enable it).

- Constrained: Provides a design preview with SDC-on-RTL constraints shown on the target nodes. This checkpoint is disabled by default (Hint: See Note below to enable it).

- Swept: Provides a design preview with unnecessary logic removed from your design.

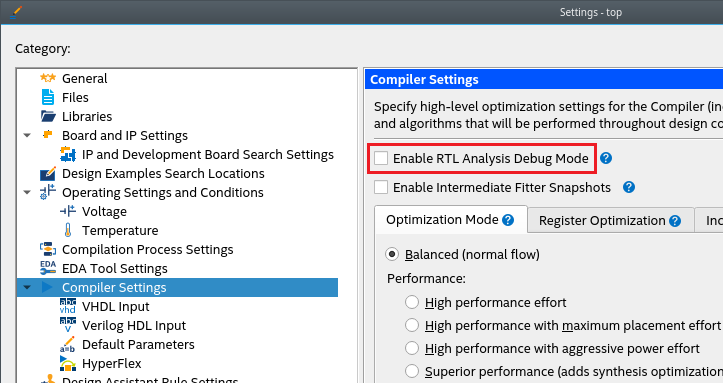

You can control the number of checkpoints generated using the RTL Analysis Debug Mode option under Project > Settings. This mode is off by default, which means only Elaborated and Swept checkpoints are available, and Instrumented and Constrained checkpoints are unavailable. When you enable this mode, all four checkpoints become available.

When the mode is off, you can obtain information about the Hierarchies Optimized Away and Top Causes for Logic Optimized Away During Sweep, under Synthesis Compilation Reports > Synthesis > Analysis & Elaboration.