Visible to Intel only — GUID: caa1684172869176

Ixiasoft

Visible to Intel only — GUID: caa1684172869176

Ixiasoft

5.1.4. Simulating the Design Example

To run a simulation, navigate to the simulation directory <example_design_directory>/sim/ed_sim/ and run the simulation script of your choice.

For ModelSim* SE and Siemens* EDA QuestaSim*- Intel FPGA Edition Simulators

- At the command prompt, change the working directory to the following:

<example_design_directory>/sim/ed_sim/mentor

- Invoke vsim by typing:

vsim

The system launches a terminal window where you can run the commands described in the following steps. - Run the following command in the terminal window:

source msim_setup.tcl

- Run the following command in the terminal window:

ld_debug

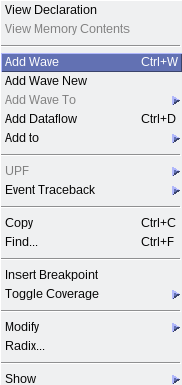

- To select a signal to observe, right-click and select Add Wave from the context menu.

- To run the simulation, type:

run -all

Upon successful completion, the simulation displays the following message:

Simulation stopped due to successful completion!

For VCS Simulator

At the command prompt, change the working directory to the following: <example_design_directory>/sim/ed_sim/synopsys/vcs

Non-interactive Mode

To run a simulation in non-interactive mode, proceed as follows:

- Type the following command on a single line:

sh vcs_setup.sh USER_DEFINED_COMPILE_OPTIONS="" USER_DEFINED_ELAB_OPTIONS="-xlrm\ uniq_prior_final" USER_DEFINED_SIM_OPTIONS=""

The system performs the simulation and displays the following message upon successful completion:

Simulation stopped due to successful completion!

Interactive Mode

To run a simulation in interactive mode, proceed as described below.

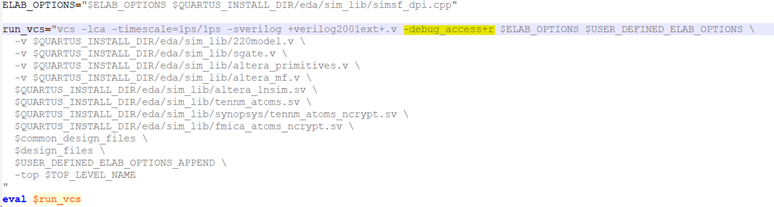

- Open the vcs_setup.sh file in an editor and add a -debug_access+r command, as highlighted in the figure below:

- Compile the design example by typing:

sh vcs_setup.sh USER_DEFINED_ELAB_OPTIONS="-xlrm\ uniq_prior_final" SKIP_SIM=1

- To start the simulation in interactive mode, type the following command in the terminal console:

simv -gui&