External Memory Interfaces (EMIF) IP User Guide: Agilex™ 5 FPGAs and SoCs

A newer version of this document is available. Customers should click here to go to the newest version.

Visible to Intel only — GUID: ewc1707950667053

Ixiasoft

Visible to Intel only — GUID: ewc1707950667053

Ixiasoft

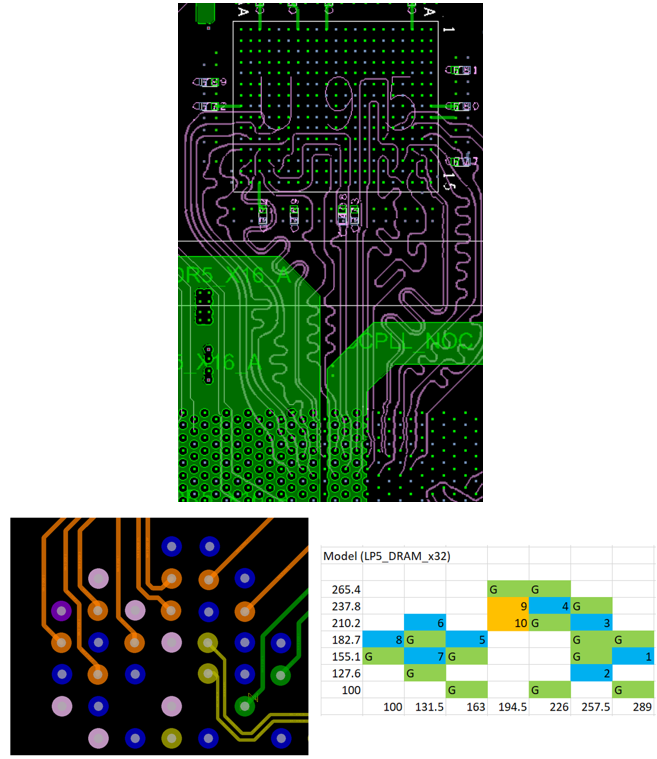

8.3.3.2. Example of an LPDDR5 Layout on an Intel FPGA Platform Board

The following figure shows the layout example of a single rank LPDDR5 x 32 bit device with pitch size of 0.7×0.8 mm in an Intel FPGA platform design. It uses a thick PCB (120mil stackup) with micro vias and through vias with backdrill. The LPDDR5 signal routing is on upper layers to avoid vertical crosstalk on interface and achieve high performance.