Visible to Intel only — GUID: dem1703180793134

Ixiasoft

Visible to Intel only — GUID: dem1703180793134

Ixiasoft

B.1. Testbench

The testbench uses a test driver module, altpcietb_bfm_rp_gen5_x16.sv, to initiate the configuration and memory transactions. At startup, the test driver module displays information from the Root Port and Endpoint Configuration Space registers, so that you can correlate to the parameters you specified using the Parameter Editor.

The example design and testbench are dynamically generated based on the configuration that you choose for the AXI Streaming Intel® FPGA IP for PCI Express* . The testbench uses the parameters that you specify in the Parameter Editor in Intel® Quartus® Prime.

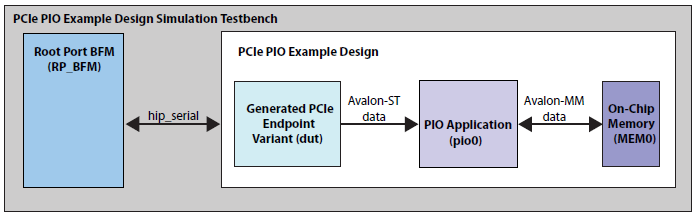

This testbench simulates a Gen5 ×16 PCI Express link using the serial PCI Express interface.

-

A configuration routine that sets up all the basic configuration registers in the Endpoint. This configuration allows the Endpoint application to be the target and initiator of PCI Express transactions.

-

A Verilog HDL procedure interface to initiate PCI Express transactions to the Endpoint.

This testbench simulates the scenario of a single Root Port talking to a single Endpoint.

The testbench uses a test driver module, altpcietb_bfm_rp_gen5_x16.sv, to initiate the configuration and memory transactions. At startup, the test driver module displays information from the Root Port and Endpoint Configuration Space registers, so that you can correlate to the parameters you specified using the Parameter Editor.

-

It is unable to generate or receive Vendor Defined Messages. Some systems generate Vendor Defined Messages. The Hard IP block simply passes these messages on to the Application Layer. Consequently, you should make the decision, based on your application, whether to design the Application Layer to process them.

-

It can only handle received read requests that are less than or equal to 256 bits or 8 DW. Many systems are capable of handling larger read requests that are then returned in multiple completions.

- It always returns a single completion for every read request. Some systems split completions on every 64-byte address boundary.

- It always returns completions in the same order the read requests were issued. Some systems generate the completions out-of-order.

-

It is unable to generate zero-length read requests that some systems generate as flush requests following some write transactions. The Application Layer must be capable of generating the completions to the zero-length read requests.

- It does not support parity.

- It does not support multi-function designs.

- It does not support Single Root I/O Virtualization (SR-IOV).