5.1. Parameter Editor Parameters

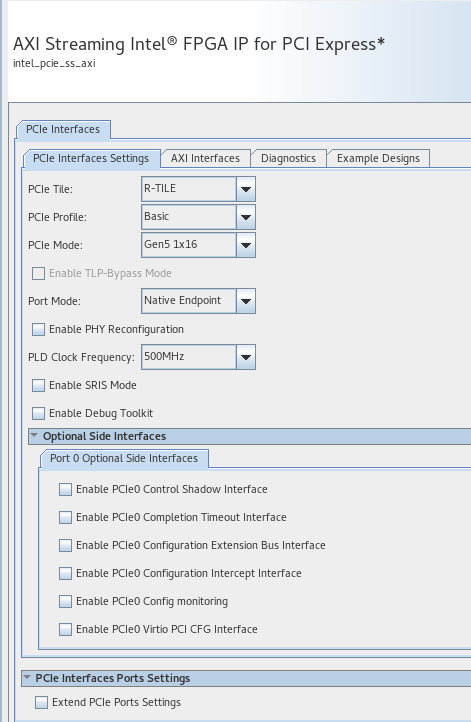

The AXI Streaming Intel® FPGA IP for PCI Express* has one tab for parameterization, the PCIe* Interfaces tab.

| Parameter | Default Setting | Parameter Description | |

|---|---|---|---|

| PCIe Interface 0 Settings | |||

| PCIe* Tile | P-Tile | Selects the supported Tile of the PCIe interface based on the device.

|

|

| PCIe* Profile | Basic | Selects functional features based on profile like virtualization, additional interfaces, number of endpoints, etc.

|

|

| PCIe* Mode | Gen4 2x8 | Selects the width of the data interface between the transaction layer and the application layer implemented in the PLD fabric, the lane data rate and the lane rate. Gen5 1x16 Gen5 2x8 Gen4 1x16 Gen4 1x8 Gen4 2x8 Gen3 1x16 Gen3 2x8 Gen3 1x8 |

|

| Enable TLP-Bypass Mode | Disabled | Enables the TLP Bypass mode. | |

| Port Mode | Native Endpoint | Selects Port Mode. For Endpoint mode with multiple ports, all ports are set to endpoint mode. | |

| Enable PHY Reconfiguration | Disabled | When on, creates an Avalon-MM slave interface that software can drive to update Transceiver reconfiguration registers. | |

| PLD Clock Frequency | 400MHz | Selects the PLD Clock Frequency. 500MHz (Gen4/Gen5) 450MHz (Gen4) 400MHz (Gen4) 350MHz (Gen4) 300MHz (Gen3) |

|

| Enable SRIS Mode | Disabled | Enables separate reference clock with independent Spread Spectrum Clocking (SSC). | |

| Enable System PLL Clock | Enabled | Enables the System PLL Clock when using F-Tile. |

|

| Enable PCS and controller user reset | Disabled | Enables PCS and controller user reset in Endpoint and Bypass modes. | |

| Enable Debug Toolkit | Disabled | Enables the Debug Toolkit. | |

| Enable CVP (Intel VSEC) | Disabled | Enablement of CVP for single tile only. | |

| Optional Side Interfaces | |||

| Enable PCIe0 Control Shadow Interface | Disabled | Enables Control Shadow Interface. Host write to specific PCIe* configuration space register's bit is indicated through this interface. | |

| Enable PCIe0 Completion Timeout Interface | Disabled | Enables Completion Timeout Interface. Completion Timeout event is indicated through this interface. | |

| Enable PCIe0 Configuration Extension Bus Interface | Disabled | Enables Configuration Extension Bus Interface. User can add additional PCIe* capabilities using this interface. | |

| PCIe* 0 Standard next address pointer for PF | 0x00000000 | This parameter is available when “Enable Configuration Extension Bus Interface” parameter is enabled. Enables CEB pointer address for PF (DW address in Hex). Valid range from 0x000 to 0x03F. | |

| PCIe* 0 Extended next address pointer for PF | 0x00000000 | This parameter is available when “Enable Configuration Extension Bus Interface” parameter is enabled. Enables CEB pointer address for PF (DW address in Hex). Valid range from 0x040 to 0x3FF. | |

| PCIe* 0 Standard next address pointer for VF | 0x00000000 | This parameter is available when “Enable Configuration Extension Bus Interface” parameter is enabled. Enables CEB pointer address for PF (DW address in Hex). Valid range from 0x000 to 0x03F. | |

| PCIe* 0 Extended next address pointer for VF | 0x00000000 | This parameter is available when “Enable Configuration Extension Bus Interface” parameter is enabled. Enables CEB pointer address for PF (DW address in Hex). Valid range from 0x040 to 0x3FF. | |

| PCIe* 0 CEB REQ to ACK Latency Timeout value | 100 | This parameter is available when “Enable Configuration Extension Bus Interface” parameter is enabled. Enables CEB REQ to ACK Latency Timeout value (in Clock Cycles). Valid range from 1 to 256. | |

| Enable PCIe* 0 Configuration Intercept Interface | Disabled | Enables Configuration Intercept Interface (CII). User can intercept PCIe* Configuration cycles using this interface (Power User Mode only). | |

| PCIe* 0 CII REQ to ACK Latency Timeout value

|

100 | This parameter is available when “Enable Configuration Intercept Interface” parameter is enabled. Enables CII REQ to ACK Latency Timeout value (in Clock Cycles). Valid range from 1 to 256. | |

| Enable PCIe0 Configuration Monitoring | Disabled | CII monitoring feature is used to monitor configuration write cycle that happens with no intention to override the values being written. When CII monitoring feature is enabled, only the st_ciireq interface are exposed to the user and not st_ciiresp. The IP decodes the CII request received and outputs it on the st_ciireq interface if it is a write request. A “cii_halt” deassertion happens towards the HIP after the shadow registers operation is done, without depending on app_ss_st_ciiresp_tvalid. | |

| Enable PCIe* 0 VirtIO PCI* CFG Interface

|

Disabled | HOST read and write accesses to VIRTIO PCI* Configuration Access Data Register will use this interface for its alternate access functionality. | |

| PCIe* Interfaces Ports Settings | |||

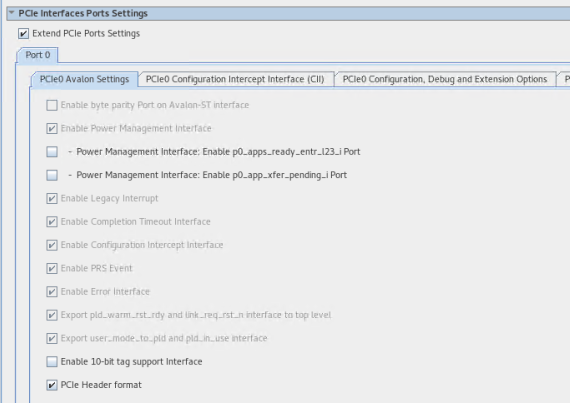

| Extend PCIe* Ports Settings | Disabled | Extends PCIe* IP Settings. When enabled, the PCIe* IP setting can be further configured. | |

| Top Level Settings | |||

| Enable ASPM Support Control | No ASPM support | Enables Active State Power Management (ASPM) Control in the Link Control Register. Valid settings are:

|

|

| Enable CVP (Intel VSEC) | Disabled | Enables Configuration Via Protocol (CVP) for a single tile only. | |

| Port 0 | |||

| PCIe0 Avalon Settings when Extend PCIe* Ports Settings=On | |||

| Enable byte parity Port on Avalon-ST interface | Disabled | Enables or disables parity Port on Avalon-ST interface. | |

| Enable Power Management Interface | Enabled | When selected, Power Management interface will be exported. | |

| Power management interface: Enable p0_apps_ready_entr_l23_i port | Disabled | When selected, input port p0_apps_ready_entr_l23_i is exposed in the Power Management interface. The application logic asserts this signal to indicate that it is ready to enter L2/L3 Ready state. It is provided for applications that must control L2/L3 Ready entry (in case certain task must be performed before going into L2/L3 Ready). | |

| Power management interface: Enable p0_app_xfer_pending_i port | Disabled | When selected, input port p0_app_xfer_pending_i is exposed in the Power Management interface. This port is used to prevent the entry to L1 or initiates the exit from L1. | |

| Enable Legacy Interrupt | Enabled | When selected, the Interrupt interface is exported. | |

| Enable Completion Timeout Interface | Enabled | Select to enable completion timeout interface. | |

| Enable Configuration Intercept Interface | Enabled | Select to enable configuration intercept interface. | |

| Enable PRS Event | Enabled | Select to enable PRS Event Interface. | |

| Enable Error Interface | Enabled | Select to enable Error Interface. | |

| Export pld_warm_rst_rdy and link_req_rst_n interface to top level | Enabled | Exports the pld_warm_rst_rdy and link_req_rst_n interface to the top level. | |

| Export user_mode_to_pld and pld_in_use interface | Enabled | Exports user_mode_to_pld and pld_in_use interface to the top level. | |

| Enable 10-bit tag support Interface | Disabled | Enables 10-bit tag support enable interface. | |

| PCIe Header Format | Enabled | When On, the P-Tile header format for PCIe is used (the first byte of the header dword is located in the most significant byte of the dword). When Off, the first byte of the header dword is located in the least significant byte of the dword. | |

| PCIe0 Configuration Intercept Interface (CII) | |||

| Enable Range 0 CII | Enabled | Indicates Physical Functions (PFs) that are subject to having Configuration cycles be intercepted or halted. Each bit refers to one PF. Together with the Range 0 Start Address and Range 0 Address Size parameters, this parameter defines the range for CII to take effect. | |

| Range 0 Start Address | 0x00000000 | Indicates the starting address where Configuration cycles can be intercepted or halted. Together with the Range 0 Address Size and Enable Range 0 CII parameters, this parameter defines the range for CII to take effect. | |

| Range 0 Address Size | 0x00000fff | Indicates the address size for Configuration cycles to be intercepted or halted. Together with the Range 0 Start Address and Enable Range 0 CII parameters, this parameter defines the range for CII to take effect. | |

| Enable Range 1 CII | Enabled | Indicates Physical Functions (PFs) that are subject to having Configuration cycles be intercepted or halted. Each bit refers to one PF. Together with the Range 1 Start Address and Range 1 Address Size parameters, this parameter defines the range for CII to take effect. | |

| Range 1 Start Address | 0x00000000 | Indicates the starting address where Configuration cycles can be intercepted or halted. Together with the Range 1 Address Size and Enable Range 1 CII parameters, this parameter defines the range for CII to take effect. | |

| Range 1 Address Size | 0x00000000 | Indicates the address size for Configuration cycles to be intercepted or halted. Together with the Range 1 Start Address and Enable Range 1 CII parameters, this parameter defines the range for CII to take effect. | |

| Enable Range 2 CII | Enabled | Indicates Physical Functions (PFs) that are subject to having Configuration cycles be intercepted or halted. Each bit refers to one PF. Together with the Range 2 Start Address and Range 2 Address Size parameters, this parameter defines the range for CII to take effect. | |

| Range 2 Start Address | 0x00000000 | Indicates the starting address where Configuration cycles can be intercepted or halted. Together with the Range 2 Address Size and Enable Range 2 CII parameters, this parameter defines the range for CII to take effect. | |

| Range 2 Address Size | 0x00000000 | Indicates the address size for Configuration cycles to be intercepted or halted. Together with the Range 2 Start Address and Enable Range 2 CII parameters, this parameter defines the range for CII to take effect. | |

| PCIe0 Configuration, Debug and Extension Options | |||

| Enable HIP dynamic reconfiguration of PCIe* registers | Enabled | When on, creates an Avalon-MM slave interface that software can drive to update global configuration registers which are read-only at run time. | |

| Gen 3 Requested equalization far-end TX preset vector | 0x00000200 | Specifies the Gen 3 requested phase 2/3 far-end TX preset vector. Choosing a value different from the default is not recommended for most designs. | |

| Gen 4 Requested equalization far-end TX preset vector | 0x00000008 | Specifies the Gen 4 requested phase 2/3 far-end TX preset vector. Choosing a value different from the default is not recommended for most designs. | |

| Gen 5 Requested equalization far-end TX preset vector | 0x00000200 | Specifies the Gen 5 requested phase 2/3 far-end TX preset vector. Choosing a value different from the default is not recommended for most designs. | |

| Predetermined Number of Lanes | 8 | Indicates the number of lanes to check for exit from Electrical Idle in Polling.Active and L2.Idle. This value is referred to as the Predetermined Number of Lanes in Section 4.2.6.2.1 of the PCIe Base Specification.

|

|

| Enable Rx Buffer Limit Ports | Disabled | When selected, RX buffer limit ports is exported for you to control RX Posted, Non-Posted and CplD Packets. Otherwise, the Max Buffer Size will be used. | |

| Bypass Posted Rx Buffer Limit

|

Disabled | When selected, the RX buffer limit selected for Posted packets is bypassed. | |

| Bypass Non-Posted Rx Buffer Limit

|

Disabled | When selected, the RX buffer limit selected for Non-Posted packets is bypassed. | |

| Bypass CplD Rx Buffer Limit

|

Disabled (Power User Mode) | When selected, the RX buffer limit selected for CplD packets is bypassed. | |

| PCIe0 Base Address Registers | |||

| PCIe0 PF0 BAR Configuration | |||

| PCIe0 PF0 BAR | |||

| BAR0 Type | 64-bit prefetchable memory | Sets the BAR type (64-bit prefetchable or 32-bit non-prefetchable). | |

| BAR0 Size | 64 Kbytes – 16 bits | Sets from 7-64 bits per base address register (BAR). | |

| BAR1 Type | Disabled | Sets the BAR type. | |

| BAR2 Type | Disabled | Sets the BAR type. | |

| BAR3 Type | Disabled | Sets the BAR type. | |

| BAR4 Type | Disabled | Sets the BAR type. | |

| BAR5 Type | Disabled | Sets the BAR type. | |

| Expansion ROM Size | Disabled | Specifies an expansion ROM from 4 KBytes - 16 MBytes when enabled. | |

| PCIe0 PF0 VF BAR | |||

| BAR0 Type | 64-bit prefetchable memory | Sets the BAR type. | |

| BAR0 Size | 64 Kbytes – 16 bits | Sets from 7-64 bits per base address register (BAR). | |

| BAR1 Type | Disabled | Sets the BAR type. | |

| BAR2 Type | Disabled | Sets the BAR type. | |

| BAR3 Type | Disabled | Sets the BAR type. | |

| BAR4 Type | Disabled | Sets the BAR type. | |

| BAR5 Type | Disabled | Sets the BAR type. | |

| Expansion ROM Size | Disabled | Specifies an expansion ROM from 4 KBytes - 16 MBytes when enabled. | |

| PCIe0 PF 1 BAR Configuration | |||

| PCIe0 PF 1 BAR | |||

| BAR0 Type | 64-bit prefetchable memory | Sets the BAR type. | |

| BAR0 Size | 64 Kbytes – 16 bits | Sets from 7-64 bits per base address register (BAR). | |

| BAR1 Type | Disabled | Sets the BAR type. | |

| BAR2 Type | Disabled | Sets the BAR type. | |

| BAR3 Type | Disabled | Sets the BAR type. | |

| BAR4 Type | Disabled | Sets the BAR type. | |

| BAR5 Type | Disabled | Sets the BAR type. | |

| Expansion ROM Size | Disabled | Specifies an expansion ROM from 4 KBytes - 16 MBytes when enabled. | |

| PCIe0 PF 1 VF BAR | |||

| BAR0 Type | 64-bit prefetchable memory | Sets the BAR type. | |

| BAR0 Size | 64 Kbytes – 16 bits | Sets from 7-64 bits per base address register (BAR). | |

| BAR1 Type | Disabled | Sets the BAR type. | |

| BAR2 Type | Disabled | Sets the BAR type. | |

| BAR3 Type | Disabled | Sets the BAR type. | |

| BAR4 Type | Disabled | Sets the BAR type. | |

| BAR5 Type | Disabled | Sets the BAR type. | |

| Expansion ROM Size | Disabled | Specifies an expansion ROM from 4 KBytes - 16 MBytes when enabled. | |

| PCIe0 PF2 BAR Configuration | |||

| PCIe0 PF 2 BAR | |||

| BAR0 Type | 64-bit prefetchable memory | Sets the BAR type. | |

| BAR0 Size | 64 Kbytes – 16 bits | Sets from 7-64 bits per base address register (BAR). | |

| BAR1 Type | Disabled | Sets the BAR type. | |

| BAR2 Type | Disabled | Sets the BAR type. | |

| BAR3 Type | Disabled | Sets the BAR type. | |

| BAR4 Type | Disabled | Sets the BAR type. | |

| BAR5 Type | Disabled | Sets the BAR type. | |

| Expansion ROM Size | Disabled | Specifies an expansion ROM from 4 KBytes - 16 MBytes when enabled. | |

| PCIe0 PF 2 VF BAR | |||

| BAR0 Type | 64-bit prefetchable memory | Sets the BAR type. | |

| BAR0 Size | 64 Kbytes – 16 bits | Sets from 7-64 bits per base address register (BAR). | |

| BAR1 Type | Disabled | Sets the BAR type. | |

| BAR2 Type | Disabled | Sets the BAR type. | |

| BAR3 Type | Disabled | Sets the BAR type. | |

| BAR4 Type | Disabled | Sets the BAR type. | |

| BAR5 Type | Disabled | Sets the BAR type. | |

| Expansion ROM Size | Disabled | Specifies an expansion ROM from 4 KBytes - 16 MBytes when enabled. | |

| PCIe 3 PF1 BAR Configuration | |||

| PCIe 3 PF1 BAR | |||

| BAR0 Type | 64-bit prefetchable memory | Sets the BAR type. | |

| BAR0 Size | 64 Kbytes – 16 bits | Sets from 7-64 bits per base address register (BAR). | |

| BAR1 Type | Disabled | Sets the BAR type. | |

| BAR2 Type | Disabled | Sets the BAR type. | |

| BAR3 Type | Disabled | Sets the BAR type. | |

| BAR4 Type | Disabled | Sets the BAR type. | |

| BAR5 Type | Disabled | Sets the BAR type. | |

| Expansion ROM Size | Disabled | Specifies an expansion ROM from 4 KBytes - 16 MBytes when enabled. | |

| PCIe 3 PF1 VF BAR | |||

| BAR0 Type | 64-bit prefetchable memory | Sets the BAR type. | |

| BAR0 Size | 64 Kbytes – 16 bits | Sets from 7-64 bits per base address register (BAR). | |

| BAR1 Type | Disabled | Sets the BAR type. | |

| BAR2 Type | Disabled | Sets the BAR type. | |

| BAR3 Type | Disabled | Sets the BAR type. | |

| BAR4 Type | Disabled | Sets the BAR type. | |

| BAR5 Type | Disabled | Sets the BAR type. | |

| Expansion ROM Size | Disabled | Specifies an expansion ROM from 4 KBytes - 16 MBytes when enabled. | |

| PCIe0 Device Identification Registers | |||

| PCIe0 PF0 IDs | |||

| Vendor ID | 0x00001172 | Sets the read-only value for the Vendor IP registers.

Note: 1172 is the Intel/Altera Vendor ID and should NOT be used by customers in production products.

|

|

| Device ID | 0x00000000 | Sets the read-only value of the Device ID register. | |

| Revision ID | 0x00000001 | Sets the read-only value of the Revision ID register. | |

| Class code | 0x00FF0000 | Sets the read-only value of the Class code register. | |

| Subsystem Vendor ID | 0x00000000 | Sets the read-only value of the AXI Streaming IP Vendor ID register. | |

| Subsystem Device ID | 0x0000000 | Sets the read-only value of the AXI Streaming IP Device ID register. | |

| PCIe0 PF0 VF IDs | |||

| Device ID | 0x00000000 | ||

| Subsystem ID | 0x00000000 | Sets the read-only value of the AXI Streaming IP ID register for the virtual functions | |

| PCIe0 PF1 IDs | |||

| Vendor ID | 0x00000000 | Sets the read-only value for the Vendor IP registers.

Note: 1172 is the Intel/Altera Vendor ID and should NOT be used by customers in production products.

|

|

| Device ID | 0x00000000 | Sets the read-only value of the Device ID register. | |

| Revision ID | 0x00000001 | Sets the read-only value of the Revision ID register. | |

| Class code | 0x00FF0000 | Sets the read-only value of the Class code register. | |

| Subsystem Vendor ID | 0x00000000 | Sets the read-only value of the AXI Streaming IP Vendor ID register. | |

| Subsystem Device ID | 0x0000000 | Sets the read-only value of the AXI Streaming IP Device ID register. | |

| PCIe0 PF1 VF IDs | |||

| Device ID | 0x00000000 | Sets the read-only value of the Device ID register for the virtual functions | |

| Subsystem ID | 0x00000000 | Sets the read-only value of the AXI Streaming IP ID register for the virtual functions. | |

| PCIe0 PF2 IDs | |||

| Vendor ID | 0x00000000 | Sets the read-only value for the Vendor IP registers.

Note: 1172 is the Intel/Altera Vendor ID and should NOT be used by customers in production products.

|

|

| Device ID | 0x00000000 | Sets the read-only value of the Device ID register. | |

| Revision ID | 0x00000001 | Sets the read-only value of the Revision ID register. | |

| Class code | 0x00FF0000 | Sets the read-only value of the Class code register. | |

| Subsystem Vendor ID | 0x00000000 | Sets the read-only value of the AXI Streaming IP Vendor ID register. | |

| Subsystem Device ID | 0x0000000 | Sets the read-only value of the AXI Streaming IP Device ID register. | |

| PCIe0 PF2 VF IDs | |||

| Device ID | 0x00000000 | Sets the read-only value of the Device ID register for the virtual functions. | |

| Subsystem ID | 0x00000000 | Sets the read-only value of the AXI Streaming IP ID register for the virtual functions. | |

| PCIe0 PF3 IDs | |||

| Vendor ID | 0x00000000 | Sets the read-only value for the Vendor IP registers.

Note: 1172 is the Intel/Altera Vendor ID and should NOT be used by customers in production products.

|

|

| Device ID | 0x00000000 | Sets the read-only value of the Device ID register. | |

| Revision ID | 0x00000001 | Sets the read-only value of the Revision ID register. | |

| Class code | 0x00FF0000 | Sets the read-only value of the Class code register. | |

| Subsystem Vendor ID | 0x00000000 | Sets the read-only value of the AXI Streaming IP Vendor ID register. | |

| Subsystem Device ID | 0x0000000 | Sets the read-only value of the AXI Streaming IP Device ID register. | |

| PCIe0 PF3 VF IDs | |||

| Device ID | 0x00000000 | Sets the read-only value of the Device ID register for the virtual functions. | |

| Subsystem ID | 0x00000000 | Sets the read-only value of the AXI Streaming IP ID register for the virtual functions. | |

| PCIe0 PCI Express* / PCI* Capabilities | |||

| PCIe0 Device | |||

| Maximum payload size supported | 512 Bytes | Sets the read-only value of the max payload size of the Device Capabilities register and optimizes for this payload size. | |

| Support Extended Tag Field | Enabled | Sets the Extended Tag Field Supported bit in Configuration Space Device Capabilities Register. | |

| PCIe0 Multifunction and SR-IOV System Settings | |||

| Enable multiple physical functions | Enabled | Enables multiple physical functions. | |

| Total physical functions (PFs) | 4 | Sets the number of physical functions. | |

| Enable SR-IOV support | Enabled | Enables SR-IOV. | |

| Total virtual functions of physical function 0 (PF0 VFs) | 0 | Sets the number of VFs to be assigned to Physical Function 0. | |

| Total virtual functions of physical function 1 (PF1 VFs) | 128 | Sets the number of VFs to be assigned to Physical Function 1. | |

| Total virtual functions of physical function 2 (PF2 VFs) | 128 | Sets the number of VFs to be assigned to Physical Function 2. | |

| Total virtual functions of physical function 3 (PF3 VFs) | 128 | Sets the number of VFs to be assigned to Physical Function 3. | |

| PCIe0 Link | |||

| Link port number (Root Port only) | 1 | Sets the read-only value of the port number field in the Link Capabilities register. | |

| Slot clock configuration | Enabled | Sets the read-only value of the slot clock configuration bit in the link status register. | |

| PCIe0 Legacy Interrupt Pin Register | |||

| PCIe0 PF0 Int Pin | |||

| Set Interrupt Pin for PF0 | NO INT | Sets interrupt Pin for PF0. | |

| PCIe0 PF1 Int Pin | |||

| Set Interrupt Pin for PF1 | NO INT | Sets interrupt Pin for PF1. | |

| PCIe0 PF2 Int Pin | |||

| Set Interrupt Pin for PF2 | NO INT | Sets interrupt Pin for PF2. | |

| PCIe0 PF3 Int Pin | |||

| Set Interrupt Pin for PF3 | NO INT | Sets interrupt Pin for PF3. | |

| PCIe0 LTR | |||

| PCIe0 Enable LTR | Disabled | LTR (Latency Tolerance Reporting) New Mechanism that enables Endpoints to send information about their latency requirements for memory reads/writes and interrupts. | |

| PCIe0 MSI | |||

| PCIe0 PF0 MSI | |||

| PF0 Enable MSI | Disabled | Enables or disables MSI capability for PF0. | |

| PF0 MSI 64-bit addressing | Disabled | Enables or disables MSI 64-bit addressing for PF0. | |

| PF0 MSI extended data capable | Disabled | Enables or disables MSI extended data capability for PF0. | |

| PF0 Number of MSI messages requested | 1 | Sets the number of messages that the application can request in the multiple messages capable field of the Message Control register. 1 2 4 8 16 32 |

|

| PCIe0 PF1 MSI | |||

| PF1 Enable MSI | Disabled | Enables or disables MSI capability for PF1. | |

| PF1 MSI 64-bit addressing | Disabled | Enables or disables MSI 64-bit addressing for PF1. | |

| PF1 MSI extended data capable | Disabled | Enables or disables MSI extended data capability for PF1 | |

| PF1 Number of MSI messages requested | 1 | Sets the number of messages that the application can request in the multiple messages capable field of the Message Control register 1 2 4 8 16 32 |

|

| PCIe0 PF2 MSI | |||

| PF2 Enable MSI | Disabled | Enables or disables MSI capability for PF2. | |

| PF2 MSI 64-bit addressing | Disabled | Enables or disables MSI 64-bit addressing for PF2. | |

| PF2 MSI extended data capable | Disabled | Enables or disables MSI extended data capability for PF2. | |

| PF2 Number of MSI messages requested | 1 | Sets the number of messages that the application can request in the multiple messages capable field of the Message Control register. 1 2 4 8 16 32 |

|

| PCIe0 PF3 MSI | |||

| PF3 Enable MSI | Disabled | Enables or disables MSI capability for PF3. | |

| PF3 MSI 64-bit addressing | Disabled | Enables or disables MSI 64-bit addressing for PF3. | |

| PF3 MSI extended data capable | Disabled | Enables or disables MSI extended data capability for PF3. | |

| PF3 Number of MSI messages requested | 1 | Sets the number of messages that the application can request in the multiple messages capable field of the Message Control register. 1 2 4 8 16 32 |

|

| PCIe0 MSI-X | |||

| PCIe0 PF MSI-X | |||

| PCIe0 PF0 MSI-X | |||

| Enable MSI-X | Enabled |

Enables or disables the MSI-X capability |

|

| Table size | 4 | Sets the number of entries in the MSI-X table. | |

| Table offset | 0x0000000000000000 | Sets the read-only base address of the MSI-X table. The low-order 3 bits are automatically set to 0. | |

| Table BAR indicator | 0 | Specifies which one of a function's base address registers, located beginning at 0x10 in the Configuration Space, maps the MSI-X table into memory space. This field is read-only. | |

| Pending bit array (PBA) offset | 0x0000000000000000 | Specifies the offset from the address stored in one of the function's base address registers that points to the base of the MSI-X PBA. This field is read-only. | |

| PBA BAR indicator | 0 | Indicates which of a function's base address registers, located beginning at 0x10 in the Configuration Space, maps the function's MSI-X PBA into memory space. This field is read-only. | |

| PCIe0 PF1 MSI-X | |||

| Enable MSI-X | Enabled |

Enables or disables the MSI-X capability |

|

| Table size | 4 | Sets the number of entries in the MSI-X table. | |

| Table offset | 0x0000000000000000 | Sets the read-only base address of the MSI-X table. The low-order 3 bits are automatically set to 0. | |

| Table BAR indicator | 0 | Specifies which one of a function's base address registers, located beginning at 0x10 in the Configuration Space, maps the MSI-X table into memory space. This field is read-only. | |

| Pending bit array (PBA) offset | 0x0000000000000000 | Specifies the offset from the address stored in one of the function's base address registers that points to the base of the MSI-X PBA. This field is read-only. | |

| PBA BAR indicator | 0 | Indicates which of a function's base address registers, located beginning at 0x10 in the Configuration Space, maps the function's MSI-X PBA into memory space. This field is read-only. | |

| PCIe0 PF2 MSI-X | |||

| Enable MSI-X | Enabled | Enables or disables the MSI-X capability |

|

| Table size | 4 | Sets the number of entries in the MSI-X table. | |

| Table offset | 0x0000000000000000 | Sets the read-only base address of the MSI-X table. The low-order 3 bits are automatically set to 0. | |

| Table BAR indicator | 0 | Specifies which one of a function's base address registers, located beginning at 0x10 in the Configuration Space, maps the MSI-X table into memory space. This field is read-only. | |

| Pending bit array (PBA) offset | 0x0000000000000000 | Specifies the offset from the address stored in one of the function's base address registers that points to the base of the MSI-X PBA. This field is read-only. | |

| PBA BAR indicator | 0 | Indicates which of a function's base address registers, located beginning at 0x10 in the Configuration Space, maps the function's MSI-X PBA into memory space. This field is read-only. | |

| PCIe0 PF3 MSI-X | |||

| Enable MSI-X | Enabled | Enables or disables the MSI-X capability |

|

| Table size | 4 | Sets the number of entries in the MSI-X table. | |

| Table offset | 0x0000000000000000 | Sets the read-only base address of the MSI-X table. The low-order 3 bits are automatically set to 0. | |

| Table BAR indicator | 0 | Specifies which one of a function's base address registers, located beginning at 0x10 in the Configuration Space, maps the MSI-X table into memory space. This field is read-only. | |

| Pending bit array (PBA) offset | 0x0000000000000000 | Specifies the offset from the address stored in one of the function's base address registers that points to the base of the MSI-X PBA. This field is read-only. | |

| PBA BAR indicator | 0 | Indicates which of a function's base address registers, located beginning at 0x10 in the Configuration Space, maps the function's MSI-X PBA into memory space. This field is read-only. | |

| PCIe0 VF MSI-X | |||

| PCIe0 PF0 VF MSI-X | |||

| Enable VF MSI-X | Enabled | Enables or disables the MSI-X capability. | |

| Table size | 4 | Sets the number of entries in the MSI-X table. | |

| Table offset | 0x0000000000000000 | Sets the read-only base address of the MSI-X table. The low-order 3 bits are automatically set to 0. | |

| Table BAR indicator | 0 | Specifies which one of a function's base address registers, located beginning at 0x10 in the Configuration Space, maps the MSI-X table into memory space. This field is read-only. | |

| Pending bit array (PBA) offset | 0x0000000000000000 | Specifies the offset from the address stored in one of the function's base address registers that points to the base of the MSI-X PBA. This field is read-only. | |

| PBA BAR indicator | 0 | Indicates which of a function's base address registers, located beginning at 0x10 in the Configuration Space, maps the function's MSI-X PBA into memory space. This field is read-only. | |

| PCIe0 PF1 VF MSI-X | |||

| Enable VF MSI-X | Enabled | Enables or disables the MSI-X capability. | |

| Table size | 4 | Sets the number of entries in the MSI-X table. | |

| Table offset | 0x0000000000000000 | Sets the read-only base address of the MSI-X table. The low-order 3 bits are automatically set to 0. | |

| Table BAR indicator | 0 | Specifies which one of a function's base address registers, located beginning at 0x10 in the Configuration Space, maps the MSI-X table into memory space. This field is read-only. | |

| Pending bit array (PBA) offset | 0x0000000000000000 | Specifies the offset from the address stored in one of the function's base address registers the points to the base of the MSI-X PBA. This field is read-only. | |

| PBA BAR indicator | 0 | Indicates which of a function's base address registers, located beginning at 0x10 in the Configuration Space, maps the function's MSI-X PBA into memory space. This field is read-only. | |

| PCIe0 PF2 VF MSI-X | |||

| Enable VF MSI-X | Enabled | Enables or disables the MSI-X capability. | |

| Table size | 4 | Sets the number of entries in the MSI-X table. | |

| Table offset | 0x0000000000000000 | Sets the read-only base address of the MSI-X table. The low-order 3 bits are automatically set to 0. | |

| Table BAR indicator | 0 | Specifies which one of a function's base address registers, located beginning at 0x10 in the Configuration Space, maps the MSI-X table into memory space. This field is read-only. | |

| Pending bit array (PBA) offset | 0x0000000000000000 | Specifies the offset from the address stored in one of the function's base address registers that points to the base of the MSI-X PBA. This field is read-only. | |

| PBA BAR indicator | 0 | Indicates which of a function's base address registers, located beginning at 0x10 in the Configuration Space, maps the function's MSI-X PBA into memory space. This field is read-only. | |

| PCIe0 PF3 VF MSI-X | |||

| Enable VF MSI-X | Enabled | Enables or disables the MSI-X capability. | |

| Table size | 4 | Sets the number of entries in the MSI-X table. | |

| Table offset | 0x0000000000000000 | Sets the read-only base address of the MSI-X table. The low-order 3 bits are automatically set to 0. | |

| Table BAR indicator | 0 | Specifies which one of a function's base address registers, located beginning at 0x10 in the Configuration Space, maps the MSI-X table into memory space. This field is read-only. | |

| Pending bit array (PBA) offset | 0x0000000000000000 | Specifies the offset from the address stored in one of the function's base address registers that points to the base of the MSI-X PBA. This field is read-only. | |

| PBA BAR indicator | 0 | Indicates which of a function's base address registers, located beginning at 0x10 in the Configuration Space, maps the function's MSI-X PBA into memory space. This field is read-only. | |

| PCIe0 PASID | |||

| PCIe0 PF0 PASID | |||

| PCIE0 PF0 Enable PASID | Enabled | PASID (Process Address Space ID) Optional feature which allows a single endpoint to be shared by multiple processes by providing each a virtual 64-bit address space. | |

| PCIe0 PF0 Enable Execute Permission Support | Disabled | Enables or disables PASID Execute Permission Support for PCIe0 PF0. | |

| PCIe0 PF0 Enable Privileged Mode Support | Disabled | Enables or disables PASID Privileged Mode Support for PCIe0 PF0. | |

| PCIe0 PF0 Max PASID Width | 0 | Sets the Max PASID Width for PCIe0 PF0. | |

| PCIe0 PF1 PASID | |||

| PCIE0 PF1 Enable PASID | Enabled | PASID (Process Address Space ID) Optional feature which allows a single endpoint to be shared by multiple processes by providing each a virtual 64-bit address space. | |

| PCIe0 PF1 Enable Execute Permission Support | Disabled | Enables or disables PASID Execute Permission Support for PCIe0 PF1. | |

| PCIe0 PF1 Enable Privileged Mode Support | Disabled | Enables or disables PASID Privileged Mode Support for PCIe0 PF1. | |

| PCIe0 PF1 Max PASID Width | 0 | Sets the Max PASID Width for PCIe0 PF1. | |

| PCIe0 PF2 PASID | |||

| PCIE0 PF2 Enable PASID | Enabled | PASID (Process Address Space ID) Optional feature which allows a single endpoint to be shared by multiple processes by providing each a virtual 64-bit address space. | |

| PCIe0 PF2 Enable Execute Permission Support | Disabled | Enables or disables PASID Execute Permission Support for PCIe0 PF2. | |

| PCIe0 PF2 Enable Privileged Mode Support | Disabled | Enables or disables PASID Privileged Mode Support for PCIe0 PF2. | |

| PCIe0 PF2 Max PASID Width | 0 | Sets the Max PASID Width for PCIe0 PF2. | |

| PCIe0 PF3 PASID | |||

| PCIE0 PF3 Enable PASID | Enabled | PASID (Process Address Space ID) Optional feature which allows a single endpoint to be shared by multiple processes by providing each a virtual 64-bit address space. | |

| PCIe0 PF3 Enable Execute Permission Support | Disabled | Enables or disables PASID Execute Permission Support for PCIe0 PF3. | |

| PCIe0 PF3 Enable Privileged Mode Support | Disabled | Enables or disables PASID Privileged Mode Support for PCIe0 PF3. | |

| PCIe0 PF3 Max PASID Width | 0 | Sets the Max PASID Width for PCIe0 PF3. | |

| PCIe0 DEV SER | |||

| Enable Device Serial Number Capability | Disabled | Enables Device Serial Number Capability (DEVSER) optional extended capability is a 64-bit value that is unique for any given PCIe* device. | |

| Device Serial Number (DW1) | Disabled | Sets the lower 32 bits of IEEE 64-bit Device Serial Number (DW1). | |

| Device Serial Number (DW2) | Disabled | Sets the upper 32 bits of IEEE 64-bit Device Serial Number (DW2). | |

| PCIe0 PRS | |||

| PCIe0 PF0 PRS | |||

| PF0 Enable PRS | Disabled | Enables PF0 Page Request Service (PRS). | |

| PCIe0 PF1 PRS | |||

| PF1 Enable PRS | Disabled | Enables PF1 Page Request Service (PRS). | |

| PCIe0 PF2 PRS | |||

| PF2 Enable PRS | Disabled | Enables PF2 Page Request Service (PRS). | |

| PCIe0 PF3 PRS | |||

| PF3 Enable PRS | Disabled | Enables PF3 Page Request Service (PRS). | |

| PCIe0 Power Management | |||

| Endpoint L0s acceptable latency | Maximum of 64ns | Sets the read-only value of the endpoint L0s acceptable latency field of the Device Capabilities register. This value should be based on the latency that the application layer can tolerate. This setting is disabled for root ports. | |

| Endpoint L1s acceptable latency | Maximum of 1 us | Sets the acceptable latency that an endpoint can withstand in the transition from the L1 to L0 state. It is an indirect measure of the endpoint internal buffering. This setting is disabled for root ports. | |

| PCIe0 VSEC | |||

| Vendor Specific Extended Capability | Disabled | Enables Vendor Specific Extended Capability (VSEC).

Note: Please enable Configuration Intercept Interface (CII) when using Vendor Specific Extended Capability

|

|

| User ID register from the Vendor Specific Extended Capability | 0x00000000 | Sets the read-only value of the 16-bit User ID register from the Vendor Specific Extended Capability | |

| Drops Vendor Type0 Messages | Disabled | When selected, received Vendor MSG Type0 will be dropped as an Unsupported Request(UR). Otherwise, received Vendor MSG Type0 will not be dropped, but visible on RX AVST interface. This option is not applicable for TLP Bypass mode. In TLP Bypass mode, received Vendor MSG Type0 will always be visible on RX AVST interface. | |

| Drops Vendor Type1 Messages | Disabled | When selected, received Vendor MSG Type1 will be dropped silently. Otherwise, received Vendor MSG Type1 will not be dropped, but visible on RX AVST interface. This option is not applicable for TLP Bypass mode. In TLP Bypass mode, received Vendor MSG Type1 will always be visible on RX AVST interface. | |

|

Note: Please enable PCIe0 Configuration Intercept Interface (CII) when using PCIe0 Vendor Specific Extended Capability.

|

|||

| PCIe0 ATS | |||

| PCIe0 ATS for Physical Functions | |||

| PCIe0 ATS for PF0 | |||

| Enable Address Translation Services (ATS) | Enabled | When Address Translation Services (ATS) is enabled, senders can request and cache translated addresses using the RP memory space for later use. | |

| PCIe0 ATS for PF1 | |||

| Enable Address Translation Services (ATS) | Enabled | When Address Translation Services (ATS) is enabled, senders can request and cache translated addresses using the RP memory space for later use. | |

| PCIe0 ATS for PF2 | |||

| Enable Address Translation Services (ATS) | Enabled | When Address Translation Services (ATS) is enabled, senders can request and cache translated addresses using the RP memory space for later use. | |

| PCIe0 ATS for PF3 | |||

| Enable Address Translation Services (ATS) | Enabled | When Address Translation Services (ATS) is enabled, senders can request and cache translated addresses using the RP memory space for later use. | |

| PCIe0 ATS for Virtual Functions | |||

| PCIe0 ATS for PF0 VF | |||

| Enable Address Translation Services (ATS) | Enabled | When Address Translation Services (ATS) is enabled, senders can request and cache translated addresses using the RP memory space for later use. | |

| PCIe0 ATS for PF1 VF | |||

| Enable Address Translation Services (ATS) | Enabled | When Address Translation Services (ATS) is enabled, senders can request and cache translated addresses using the RP memory space for later use. | |

| PCIe0 ATS for PF2 VF | |||

| Enable Address Translation Services (ATS) | Enabled | When Address Translation Services (ATS) is enabled, senders can request and cache translated addresses using the RP memory space for later use. | |

| PCIe0 ATS for PF3 VF | |||

| Enable Address Translation Services (ATS) | Enabled | When Address Translation Services (ATS) is enabled, senders can request and cache translated addresses using the RP memory space for later use. | |

| PCIe0 TPH | |||

| PCIe0 TPH for Physical Functions | |||

| PCIe0 TPH for PF0 | |||

| Enable TLP Processing Hints (TPH) | Enabled | Using TLP Processing Hints (TPH) may improve latency and traffic congestion. | |

| PCIe0 TPH for PF1 | |||

| Enable TLP Processing Hints (TPH) | Enabled | Using TLP Processing Hints (TPH) may improve latency and traffic congestion. | |

| PCIe0 TPH for PF2 | |||

| Enable TLP Processing Hints (TPH) | Enabled | Using TLP Processing Hints (TPH) may improve latency and traffic congestion. | |

| PCIe0 TPH for PF3 | |||

| Enable TLP Processing Hints (TPH) | Enabled | Using TLP Processing Hints (TPH) may improve latency and traffic congestion. | |

| PCIe0 TPH for Virtual Functions | |||

| PCIe0 TPH for PF0 VF | |||

| Enable TLP Processing Hints (TPH) | Enabled | Using TLP Processing Hints (TPH) may improve latency and traffic congestion. | |

| PCIe0 TPH for PF1 VF | |||

| Enable TLP Processing Hints (TPH) | Enabled | Using TLP Processing Hints (TPH) may improve latency and traffic congestion. | |

| PCIe0 TPH for PF2 VF | |||

| Enable TLP Processing Hints (TPH) | Enabled | Using TLP Processing Hints (TPH) may improve latency and traffic congestion. | |

| PCIe0 TPH for PF3 VF | |||

| Enable TLP Processing Hints (TPH) | Enabled | Using TLP Processing Hints (TPH) may improve latency and traffic congestion. | |

| PCIe0 ACS Capabilities | |||

| PCIe0 ACS for Physical Functions | |||

| PCIe0 ACS for PF0 | |||

| Enable Access Control Service (ACS) | Disabled | ACS defines a set of control points within a PCI Express* topology to determine whether a TLP is to be routed normally, blocked, or redirected. | |

| Enable ACS P2P Traffic Support | Disabled | Indicates if the component supports Peer to Peer Traffic. | |

| Enable ACS P2P Egress Control

|

Disabled | Indicates if the component implements ACS P2P Egress Control. | |

| PCIe0 ACS for PF1 | |||

| Enable Access Control Service (ACS) | Disabled | ACS defines a set of control points within a PCI Express* topology to determine whether a TLP is to be routed normally, blocked, or redirected. | |

| Enable ACS P2P Traffic Support | Disabled | Indicates if the component supports Peer to Peer Traffic. | |

| Enable ACS P2P Egress Control

|

Disabled | Indicates if the component implements ACS P2P Egress Control. | |

| PCIe0 ACS for PF2 | |||

| Enable Access Control Service (ACS) | Disabled | ACS defines a set of control points within a PCI Express* topology to determine whether a TLP is to be routed normally, blocked, or redirected. | |

| Enable ACS P2P Traffic Support | Disabled | Indicates if the component supports Peer to Peer Traffic. | |

| Enable ACS P2P Egress Control

|

Disabled | Indicates if the component implements ACS P2P Egress Control. | |

| PCIe0 ACS for PF3 | |||

| Enable Access Control Service (ACS) | Disabled | ACS defines a set of control points within a PCI Express* topology to determine whether a TLP is to be routed normally, blocked, or redirected. | |

| Enable ACS P2P Traffic Support | Disabled | Indicates if the component supports Peer to Peer Traffic. | |

| Enable ACS P2P Egress Control

|

Disabled | Indicates if the component implements ACS P2P Egress Control. | |

| PCIe0 ACS for Virtual Functions | |||

| PCIe0 ACS for PF0 VF | |||

| Enable Access Control Service (ACS) | Disabled | ACS defines a set of control points within a PCI Express* topology to determine whether a TLP is to be routed normally, blocked, or redirected. | |

| PCIe0 ACS for PF1 VF | |||

| Enable Access Control Service (ACS) | Disabled | ACS defines a set of control points within a PCI Express* topology to determine whether a TLP is to be routed normally, blocked, or redirected. | |

| PCIe0 ACS for PF2 VF | |||

| Enable Access Control Service (ACS) | Disabled | ACS defines a set of control points within a PCI Express* topology to determine whether a TLP is to be routed normally, blocked, or redirected. | |

| PCIe0 ACS for PF3 VF | |||

| Enable Access Control Service (ACS) | Disabled | ACS defines a set of control points within a PCI Express* topology to determine whether a TLP is to be routed normally, blocked, or redirected. | |

| PCIe0 VIRTIO | |||

| Enable VIRTIO support | Enabled | If set, enables VIRTIO Capabilities for PFs and VFs. | |

| PCIe0 PF0 VIRTIO STRUCTURES | |||

| Enable VIRTIO Capabilities for PF0 | Disabled | Exposes VIRTIO Capabilities for VIRTIO Capable Devices. | |

| Enable Device Specific Capability for PF0 | Enabled | Enables Device Specific Capability for VIRTIO Device on PF0. | |

| PCIe0 PF0 COMMON CONFIGURATION STRUCTURE | |||

| BAR Indicator | Disabled | Indicates BAR holding the Common Configuration Structure. | |

| Offset within BAR | Disabled | Indicates starting position of Common Config Structure in given BAR. | |

| Structure Length in Bytes | Disabled | Indicates length of Common Config Structure. | |

| PCIe0 PF0 NOTIFICATION STRUCTURE | |||

| BAR Indicator | Disabled | Indicates BAR holding the Notification Structure. | |

| Offset within BAR | Disabled | Indicates starting position of Notification Structure in given BAR. | |

| Structure Length in Bytes | Disabled | Indicates length of Notification Structure. | |

| Notify Off Multiplier | Disabled | Indicates Multiplier for queue_notify_off. | |

| PCIe0 PF0 ISR STATUS STRUCTURE | |||

| BAR Indicator | Disabled | Indicates BAR holding the ISR STATUS Structure. | |

| Offset within BAR | Disabled | Indicates starting position of ISR STATUS Structure in given BAR. | |

| Structure Length in Bytes | Disabled | Indicates length of ISR STATUS Structure. | |

| PCIe0 PF0 PCI CONFIGURATION ACCESS STRUCTURE | |||

| BAR Indicator | Disabled | Indicates BAR holding the PCI Configuration Access Structure. | |

| Offset within BAR | Disabled | Indicates starting position of PCI Configuration Access Structure in given BAR. | |

| Structure Length in Bytes | Disabled | Indicates length of PCI Configuration Access Structure. | |

|

Note: BAR Indicator, Offset within BAR and Structure Length are 0 by default.

|

|||

| PCIe0 PF1 VIRTIO STRUCTURES | |||

| Enable VIRTIO Capabilities for PF1 | Enabled | Exposes VIRTIO Capabilities for VIRTIO Capable Devices. | |

| Enable Device Specific Capability for PF1 | Enabled | Enables Device Specific Capability for VIRTIO Device on PF1. | |

| PCIe0 PF1 COMMON CONFIGURATION STRUCTURE | |||

| BAR Indicator | Disabled | Indicates BAR holding the Common Configuration Structure. | |

| Offset within BAR | Disabled | Indicates starting position of Common Configuration Structure in given BAR. | |

| Structure Length in Bytes | Disabled | Indicates length of Common Configuration Structure. | |

| PCIe0 PF1 NOTIFICATION STRUCTURE | |||

| BAR Indicator | Disabled | Indicates BAR holding the Notification Structure. | |

| Offset within BAR | Disabled | Indicates starting position of Notification Structure in given BAR. | |

| Structure Length in Bytes | Disabled | Indicates length of Notification Structure. | |

| Notify Off Multiplier | Disabled | Indicates Multiplier for queue_notify_off. | |

| PCIe0 PF1 ISR STATUS STRUCTURE | |||

| BAR Indicator | Disabled | Indicates BAR holding the ISR STATUS Structure. | |

| Offset within BAR | Disabled | Indicates starting position of ISR STATUS Structure in given BAR. | |

| Structure Length in Bytes | Disabled | Indicates length of ISR STATUS Structure. | |

| PCIe0 PF1 PCI CONFIGURATION ACCESS STRUCTURE | |||

| BAR Indicator | Disabled | Indicates BAR holding the PCI Configuration Access Structure. | |

| Offset within BAR | Disabled | Indicates starting position of PCI Configuration Access Structure in given BAR. | |

| Structure Length in Bytes | Disabled | Indicates length of PCI Configuration Access Structure. | |

|

Note: BAR Indicator, Offset within BAR and Structure Length are 0 by default.

|

|||

| PCIe0 PF2 VIRTIO STRUCTURES | |||

| Enable VIRTIO Capabilities for PF2 | Enabled | Exposes VIRTIO Capabilities for VIRTIO Capable Devices. | |

| Enable Device Specific Capability for PF2 | Enabled | Enables Device Specific Capability for VIRTIO Device on PF2. | |

| PCIe0 PF2 COMMON CONFIGURATION STRUCTURE | |||

| BAR Indicator | 0 | Indicates BAR holding the Common Configuration Structure. | |

| Offset within BAR | 0x00000000 | Indicates starting position of Common Configuration Structure in given BAR. | |

| Structure Length in Bytes | 0x00000000 | Indicates length of Common Configuration Structure. | |

| PCIe0 PF2 NOTIFICATION STRUCTURE | |||

| BAR Indicator | 0 | Indicates BAR holding the Notification Structure. | |

| Offset within BAR | 0x00000000 | Indicates starting position of Notification Structure in given BAR. | |

| Structure Length in Bytes | 0x00000000 | Indicates length of Notification Structure. | |

| Notify Off Multiplier | 0x00000000 | Indicates Multiplier for queue_notify_off. | |

| PCIe0 PF2 ISR STATUS STRUCTURE | |||

| BAR Indicator | 0 | Indicates BAR holding the ISR STATUS Structure. | |

| Offset within BAR | 0x00000000 | Indicates starting position of ISR STATUS Structure in given BAR. | |

| Structure Length in Bytes | 0x00000000 | Indicates length of ISR STATUS Structure. | |

| PCIe0 PF2 DEVICE SPECIFIC STRUCTURE | |||

| BAR Indicator | 0 | Indicates BAR holding the Device Specific Structure. | |

| Offset within BAR | 0x00000000 | Indicates starting position of Device Specific Structure in given BAR. | |

| Structure Length in Bytes | 0x00000000 | Indicates length of Device Specific Structure. | |

| PCIe0 PF2 PCI CONFIGURATION ACCESS STRUCTURE | |||

| BAR Indicator | 0 | Indicates BAR holding the PCI Configuration Access Structure. | |

| Offset within BAR | 0x00000000 | Indicates starting position of PCI Configuration Access Structure in given BAR. | |

| Structure Length in Bytes | 0x00000000 | Indicates length of PCI Configuration Access Structure. | |

|

Note: BAR Indicator, Offset within BAR and Structure Length are 0 by default.

|

|||

| PCIe0 PF 3 VIRTIO STRUCTURES | |||

| Enable VIRTIO Capabilities for PF3 | Enabled | Exposes VIRTIO Capabilities for VIRTIO Capable Devices. | |

| Enable Device Specific Capability for PF3 | Enabled | Enables Device Specific Capability for VIRTIO Device on PF3. | |

| PCIe0 PF3 COMMON CONFIGURATION STRUCTURE | |||

| BAR Indicator | 0 | Indicates BAR holding the Common Configuration Structure. | |

| Offset within BAR | 0x00000000 | Indicates starting position of Common Configuration Structure in given BAR. | |

| Structure Length in Bytes | 0x00000000 | Indicates length of Common Configuration Structure. | |

| PCIe0 PF3 NOTIFICATION STRUCTURE | |||

| BAR Indicator | 0 | Indicates BAR holding the Notification Structure. | |

| Offset within BAR | 0x00000000 | Indicates starting position of Notification Structure in given BAR. | |

| Structure Length in Bytes | 0x00000000 | Indicates length of Notification Structure. | |

| Notify Off Multiplier | 0x00000000 | Indicates Multiplier for queue_notify_off. | |

| PCIe0 PF3 ISR STATUS STRUCTURE | |||

| BAR Indicator | 0 | Indicates BAR holding the ISR STATUS Structure. | |

| Offset within BAR | 0x00000000 | Indicates starting position of ISR STATUS Structure in given BAR. | |

| Structure Length in Bytes | 0x00000000 | Indicates length of ISR STATUS Structure. | |

| PCIe0 PF3 DEVICE SPECIFIC STRUCTURE | |||

| BAR Indicator | 0 | Indicates BAR holding the Device Specific Structure. | |

| Offset within BAR | 0x00000000 | Indicates starting position of Device Specific Structure in given BAR. | |

| Structure Length in Bytes | 0x00000000 | Indicates length of Device Specific Structure. | |

| PCIe0 PF3 PCI CONFIGURATION ACCESS STRUCTURE | |||

| BAR Indicator | 0 | Indicates BAR holding the PCI Configuration Access Structure. | |

| Offset within BAR | 0x00000000 | Indicates starting position of PCI Configuration Access Structure in given BAR. | |

| Structure Length in Bytes | 0x00000000 | Indicates length of PCI Configuration Access Structure. | |

|

Note: BAR Indicator, Offset within BAR and Structure Length are 0 by default.

|

|||

| PCIe0 PF0 VFs VIRTIO STRUCTURES | |||

| Enable VIRTIO Capabilities for PF0 VFs | Enabled | Exposes VIRTIO Capabilities for VIRTIO Capable Devices. | |

| Enable Device Specific Capability for PF0 VFs | Enabled | Enables Device Specific Capability for VIRTIO Device on PF1 VFs. | |

| PCIe0 PF0 VFs COMMON CONFIGURATION STRUCTURE | |||

| BAR Indicator | 0 | Indicates BAR holding the Common Configuration Structure. | |

| Offset within BAR | 0x00000000 | Indicates starting position of Common Configuration Structure in given BAR. | |

| Structure Length in Bytes | 0x00000000 | Indicates length of Common Configuration Structure. | |

| PCIe0 PF0 VFs NOTIFICATION STRUCTURE | |||

| BAR Indicator | 0 | Indicates BAR holding the Notification Structure. | |

| Offset within BAR | 0x00000000 | Indicates starting position of Notification Structure in given BAR. | |

| Structure Length in Bytes | 0x00000000 | Indicates length of Notification Structure. | |

| Notify Off Multiplier | 0x00000000 | Indicates Multiplier for queue_notify_off. | |

| PCIe0 PF0 VFs ISR STATUS STRUCTURE | |||

| BAR Indicator | 0 | Indicates BAR holding the ISR STATUS Structure. | |

| Offset within BAR | 0x00000000 | Indicates starting position of ISR STATUS Structure in given BAR. | |

| Structure Length in Bytes | 0x00000000 | Indicates length of ISR STATUS Structure. | |

| PCIe0 PF0 VFs DEVICE SPECIFIC STRUCTURE | |||

| BAR Indicator | 0 | Indicates BAR holding the Device Specific Structure. | |

| Offset within BAR | 0x00000000 | Indicates starting position of Device Specific Structure in given BAR. | |

| Structure Length in Bytes | 0x00000000 | Indicates length of Device Specific Structure. | |

| PCIe0 PF0 VFs PCI CONFIGURATION ACCESS STRUCTURE | |||

| BAR Indicator | 0 | Indicates BAR holding the PCI Configuration Access Structure. | |

| Offset within BAR | 0x00000000 | Indicates starting position of PCI Configuration Access Structure in given BAR. | |

| Structure Length in Bytes | 0x00000000 | Indicates length of PCI Configuration Access Structure. | |

|

Note: BAR Indicator, Offset within BAR and Structure Length are 0 by default.

|

|||

| PCIe0 PF1 VFs VIRTIO STRUCTURES | |||

| Enable VIRTIO Capabilities for PF1 | Enabled | Exposes VIRTIO Capabilities for VIRTIO Capable Devices. | |

| Enable Device Specific Capability for PF1 | Enabled | Enables Device Specific Capability for VIRTIO Device on PF2 VFs. | |

| PCIe0 PF1 VFs COMMON CONFIGURATION STRUCTURE | |||

| BAR Indicator | 0 | Indicates BAR holding the Common Configuration Structure. | |

| Offset within BAR | 0x00000000 | Indicates starting position of Common Configuration Structure in given BAR. | |

| Structure Length in Bytes | 0x00000000 | Indicates length of Common Configuration Structure. | |

| PCIe0 PF1 VFs NOTIFICATION STRUCTURE | |||

| BAR Indicator | 0 | Indicates BAR holding the Notification Structure. | |

| Offset within BAR | 0x00000000 | Indicates starting position of Notification Structure in given BAR. | |

| Structure Length in Bytes | 0x00000000 | Indicates length of Notification Structure. | |

| Notify Off Multiplier | 0x00000000 | Indicates Multiplier for queue_notify_off. | |

| PCIe0 PF1 VFs ISR STATUS STRUCTURE | |||

| BAR Indicator | 0 | Indicates BAR holding the ISR STATUS Structure. | |

| Offset within BAR | 0x00000000 | Indicates starting position of ISR STATUS Structure in given BAR. | |

| Structure Length in Bytes | 0x00000000 | Indicates length of ISR STATUS Structure. | |

| PCIe0 PF1 VFs DEVICE SPECIFIC STRUCTURE | |||

| BAR Indicator | 0 | Indicates BAR holding the Device Specific Structure. | |

| Offset within BAR | 0x00000000 | Indicates starting position of Device Specific Structure in given BAR. | |

| Structure Length in Bytes | 0x00000000 | Indicates length of Device Specific Structure. | |

| PCIe0 PF1 VFs PCI CONFIGURATION ACCESS STRUCTURE | |||

| BAR Indicator | 0 | Indicates BAR holding the PCI Configuration Access Structure. | |

| Offset within BAR | 0x00000000 | Indicates starting position of PCI Configuration Access Structure in given BAR. | |

| Structure Length in Bytes | 0x00000000 | Indicates length of PCI Configuration Access Structure. | |

|

Note: BAR Indicator, Offset within BAR and Structure Length are 0 by default.

|

|||

| PCIe0 PF2 VFs VIRTIO STRUCTURES | |||

| Enable VIRTIO Capabilities for PF2 | Enabled | Exposes VIRTIO Capabilities for VIRTIO Capable Devices. | |

| Enable Device Specific Capability for PF2 | Enabled | Enables Device Specific Capability for VIRTIO Device on PF3 VFs. | |

| PCIe0 PF2 VFs COMMON CONFIGURATION STRUCTURE | |||

| BAR Indicator | 0 | Indicates BAR holding the Common Configuration Structure. | |

| Offset within BAR | 0x00000000 | Indicates starting position of Common Configuration Structure in given BAR. | |

| Structure Length in Bytes | 0x00000000 | Indicates length of Common Configuration Structure. | |

| PCIe0 PF2 VFs NOTIFICATION STRUCTURE | |||

| BAR Indicator | 0 | Indicates BAR holding the Notification Structure. | |

| Offset within BAR | 0x00000000 | Indicates starting position of Notification Structure in given BAR. | |

| Structure Length in Bytes | 0x00000000 | Indicates length of Notification Structure. | |

| Notify Off Multiplier | 0x00000000 | Indicates Multiplier for queue_notify_off. | |

| PCIe0 PF2 VFs ISR STATUS STRUCTURE | |||

| BAR Indicator | 0 | Indicates BAR holding the ISR STATUS Structure. | |

| Offset within BAR | 0x00000000 | Indicates starting position of ISR STATUS Structure in given BAR. | |

| Structure Length in Bytes | 0x00000000 | Indicates length of ISR STATUS Structure. | |

| PCIe0 PF2 VFs DEVICE SPECIFIC STRUCTURE | |||

| BAR Indicator | 0 | Indicates BAR holding the Device Specific Structure. | |

| Offset within BAR | 0x00000000 | Indicates starting position of Device Specific Structure in given BAR. | |

| Structure Length in Bytes | 0x00000000 | Indicates length of Device Specific Structure. | |

| PCIe0 PF2 VFs PCI CONFIGURATION ACCESS STRUCTURE | |||

| BAR Indicator | 0 | Indicates BAR holding the PCI Configuration Access Structure. | |

| Offset within BAR | 0x00000000 | Indicates starting position of PCI Configuration Access Structure in given BAR. | |

| Structure Length in Bytes | 0x00000000 | Indicates length of PCI Configuration Access Structure. | |

|

Note: BAR Indicator, Offset within BAR and Structure Length are 0 by default.

|

|||

| PCIe0 PF3 VFs VIRTIO STRUCTURES | |||

| Enable VIRTIO Capabilities for PF3 | Enabled | Exposes VIRTIO Capabilities for VIRTIO Capable Devices. | |

| Enable Device Specific Capability for PF3 | Enabled | Enables Device Specific Capability for VIRTIO Device on PF3 VFs. | |

| PCIe0 PF3 VFs COMMON CONFIGURATION STRUCTURE | |||

| BAR Indicator | 0 | Indicates BAR holding the Common Configuration Structure. | |

| Offset within BAR | 0x00000000 | Indicates starting position of Common Configuration Structure in given BAR. | |

| Structure Length in Bytes | 0x00000000 | Indicates length of Common Configuration Structure. | |

| PCIe0 PF3 VFs NOTIFICATION STRUCTURE | |||

| BAR Indicator | 0 | Indicates BAR holding the Notification Structure. | |

| Offset within BAR | 0x00000000 | Indicates starting position of Notification Structure in given BAR. | |

| Structure Length in Bytes | 0x00000000 | Indicates length of Notification Structure. | |

| Notify Off Multiplier | 0x00000000 | Indicates Multiplier for queue_notify_off. | |

| PCIe0 PF3 VFs ISR STATUS STRUCTURE | |||

| BAR Indicator | 0 | Indicates BAR holding the ISR STATUS Structure. | |

| Offset within BAR | 0x00000000 | Indicates starting position of ISR STATUS Structure in given BAR. | |

| Structure Length in Bytes | 0x00000000 | Indicates length of ISR STATUS Structure. | |

| PCIe0 PF3 VFs DEVICE SPECIFIC STRUCTURE | |||

| BAR Indicator | 0 | Indicates BAR holding the Device Specific Structure. | |

| Offset within BAR | 0x00000000 | Indicates starting position of Device Specific Structure in given BAR. | |

| Structure Length in Bytes | 0x00000000 | Indicates length of Device Specific Structure. | |

| PCIe0 PF3 VFs PCI CONFIGURATION ACCESS STRUCTURE | |||

| BAR Indicator | 0 | Indicates BAR holding the PCI Configuration Access Structure. | |

| Offset within BAR | 0x00000000 | Indicates starting position of PCI Configuration Access Structure in given BAR. | |

| Structure Length in Bytes | 0x00000000 | Indicates length of PCI Configuration Access Structure. | |

|

Note: BAR Indicator, Offset within BAR and Structure Length are 0 by default.

|

|||

| Parameter | Default Setting | Parameter Description |

|---|---|---|

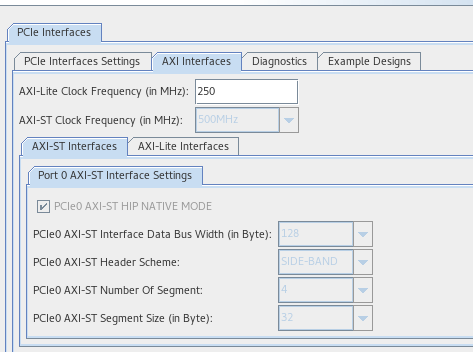

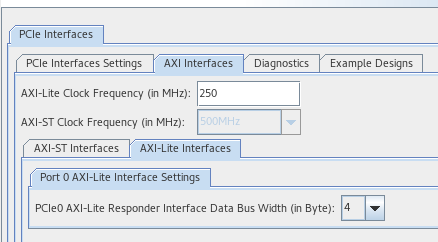

| AXI Streaming Configuration | ||

| AXI Interfaces | ||

| AXI-Lite Clock Frequency (in MHz) | 250 | Selects the PCIe* IP AXI-Lite Operating Clock Frequency.

|

| AXI-ST Clock Frequency (in MHz) | 470 | Selects the PCIe* IP AXI-ST Operating Clock Frequency. 500 (Gen5/4) 470 (Gen5/4) 400 (Gen5/4) 350 (Gen5/4) 250 (Gen3) |

| AXI-ST Interfaces | ||

| Port 0 AXI-ST Interface 0 Settings | ||

| PCIe0 AXI-ST Interface Data Bus Width (in Byte) | 64 | Selects application's AXI streaming data bus width. The interface width is defined in terms of number of Bytes.

|

| PCIe0 AXI-ST HIP Native mode | Enabled | Available only for R-Tile. When enabled, the IP enables the configuration supported natively by the HIP's AVST interface for interface width, segment size, AXI-ST clock frequency and AXI-ST header interface type combinations. When disabled, you can choose the AXI-ST interface width, segment size, header interface type and clock frequency.

Note: Only the HIP Native mode is supported in the current release.

|

| PCIe0 AXI-ST Header scheme | Sideband |

Selects the AXI-ST header scheme. The following schemes are available:

Note: Only the sideband header scheme is supported in the current release.

|

| PCIe0 AXI-ST number of segments | 4,2,1 | Selects the number of segments available on the AXI-ST interface. Indicates simple packing when the number of segments equals 1 and compact packing when the number of segments equals 2 or 4. |

| PCIe0 AXI-ST Segment Size (in Byte) | 32 | Indicates smallest fragment of Data bus when it is divided into multiple segments. This allows start of packet at different positions on data bus

|

| AXI-Lite Interfaces | ||

| Port 0 AXI-Lite Interface Settings | ||

| PCIe0 AXI-Lite Responder Interface Data Bus Width (in Byte) | 4 | Selects application's AXI-Lite Responder interface's data bus width. The interface width is defined in terms of number of Bytes

|

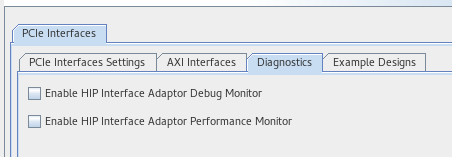

| Parameter | Default Setting | Parameter Description |

|---|---|---|

| Enable HIP Interface Adaptor Debug Monitor | False | Enables the HIP Interface Adaptor Debug Monitor.

|

| Enable HIP Interface Adaptor Performance Monitor | False | Enables the HIP Interface Adaptor Performance Monitor.

|

| Parameter | Default Setting | Parameter Description |

|---|---|---|

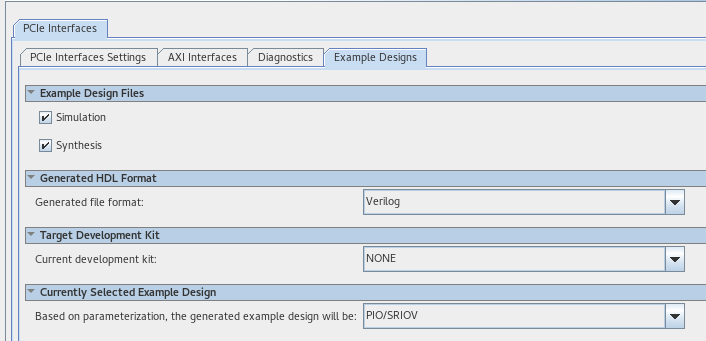

| Simulation | True | When checked, all necessary filesets for simulation will be generated. Otherwise, a Platform Designer example design system will be generated. |

| Synthesis | True | When checked, all necessary filesets for synthesis will be generated. Otherwise, a Platform Designer example design system will be generated. |

| Generated HDL format | Verilog | HDL format. Currently, only Verilog is available. |

| Target development kit | None Intel Agilex® 7 I-Series FPGA DevKit DK-DEV-AGI027R1BES |

Provides support for various Development Kits listed. If an Intel FPGA Development Kit is selected, the Target Device used for generation will be the one that matches the device on the Development Kit. |

| Currently Selected Example Design | PIO/SRIOV | Only the PIO design example is available in the current release of Intel® Quartus® Prime. |