Visible to Intel only — GUID: vht1696533000719

Ixiasoft

Visible to Intel only — GUID: vht1696533000719

Ixiasoft

5.6. Transaction Size

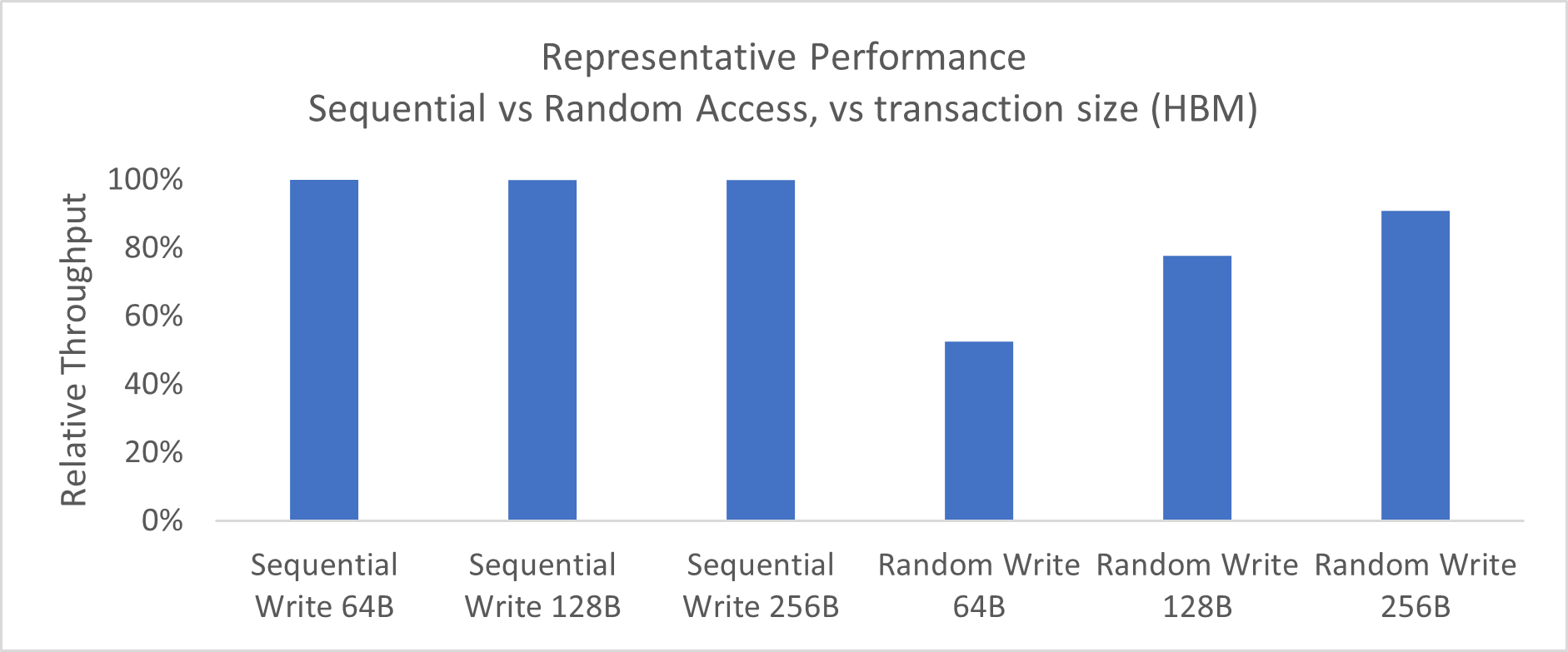

The transaction size that you use at the NoC initiators significantly impacts performance. Short transactions of less than 64 bytes do not make efficient use of the 64 byte native packet size on the NoC. For short transactions, part of the packet is unused, wasting that bandwidth. Issue transactions with corresponding AxLEN to ensure that multiples of 64 bytes are carried. This means the transaction must have AxLEN of at least 1 (two beat burst) if you are using the 256-bit mode of the initiator. Always use AxSIZE to fill the entire data width of the interface.

Transaction size at the memory controller also impacts the ability of the controller to issue efficient transactions to the memory. Although the NoC divides transactions into 64-byte segments, the memory controller uses its transaction queue to issue transactions efficiently.

Long transactions tend to populate the queue with transactions that have related addresses that the controller can service efficiently. Using longer transaction sizes has the effect of reducing the effective randomness of addresses, which can lead to better memory controller efficiency.

Using large transaction sizes also reduces the impact of the initiator maximum outstanding transaction limit. Generally, using 128-byte or 256-byte transactions maximizes the throughput of the NoC, with diminishing returns at larger transaction sizes.