Visible to Intel only — GUID: vna1696538418039

Ixiasoft

Visible to Intel only — GUID: vna1696538418039

Ixiasoft

5.13. Example: 2x2 HBM Crossbars

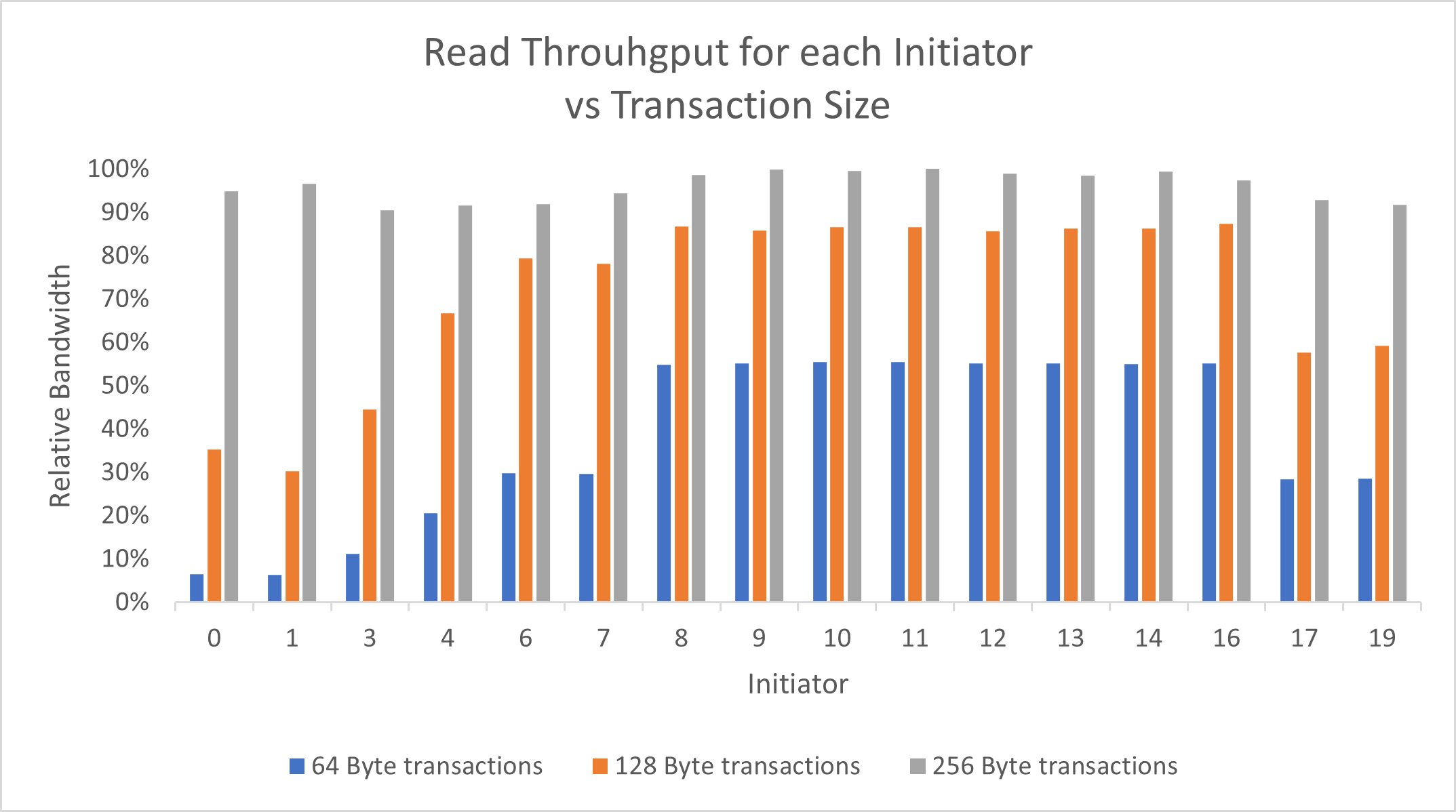

Consider a scenario of 2x2 HBM crossbars using the layout that Recommended NoC Design Topologies describes. With 64 byte, random read traffic, significant congestion develops on the NOC, some initiators hit their maximum outstanding transaction limit, and the initiators on the sides are starved.

You can alleviate the problem significantly by increasing the transaction size. Read Throughput for Each Initiator Versus Transaction Size illustrates throughput on each initiator, with different values of transaction size.

By increasing transaction size, you can make the accesses at the memory controller less random over short sequences which greatly increases memory controller efficiency. You can also reduce the number of tracked transactions, so the initiators are not limited by the maximum number of outstanding transactions.