Visible to Intel only — GUID: mgb1535594411762

Ixiasoft

5.3.1. The Configure Menu

5.3.2. The Sys Info Tab

5.3.3. The QSFP Tab

5.3.4. The PCIE Tab

Status

Port

PMA Setting

Data Type

Error Control

Loopback

5.3.5. The Component DDR4 Tab

5.3.6. The HiLo DDR4 Tab

5.3.7. The DDR4 Dimm Tab

5.3.8. The HBM2 Top Tab

5.3.9. The HBM2 Bottom Tab

5.3.10. Power Monitor

5.3.11. Clock Controller

Visible to Intel only — GUID: mgb1535594411762

Ixiasoft

5.3.4. The PCIE Tab

This tab allows you to run a PCIe* loopback test on your board. You can also load the design and use an oscilloscope to measure an eye diagram of the PCIe* transmit signals.

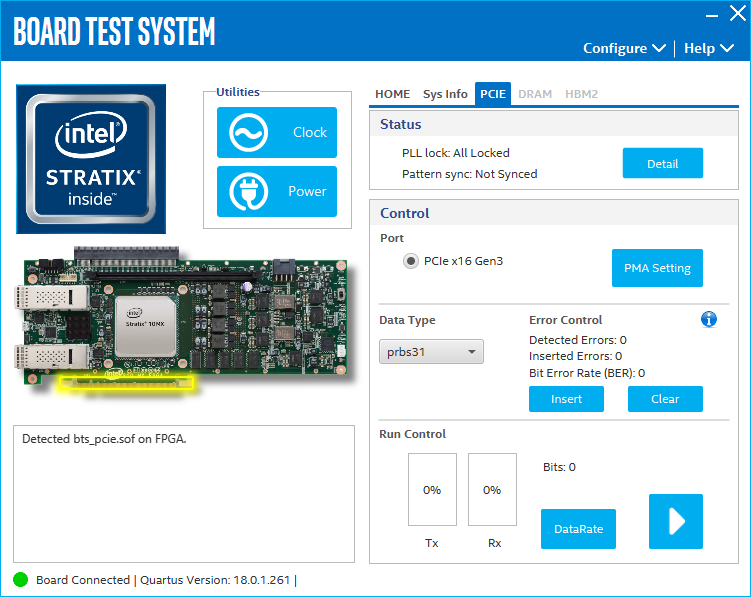

Figure 25. The PCIE Tab

The following sections describe the controls on the PCIE tab.

Status

Displays the following status information during a loopback test:

- PLL Lock: Shows the PLL locked or unlocked state.

- Pattern sync: Shows the pattern synced or not synced state. The pattern is considered synced when the start of the data sequence is detected.

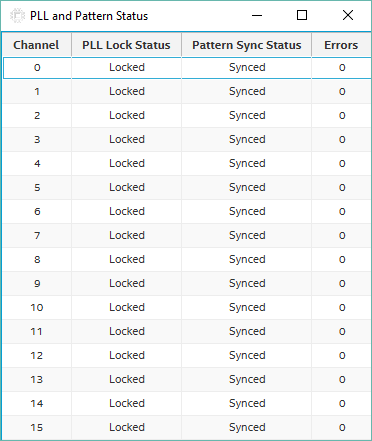

- Details: Shows the PLL lock and pattern sync status:

Port

PCIe* x16 Gen3

PMA Setting

Allows you to make changes to the PMA parameters that affect the active transceiver interface. The following settings are available for analysis:

- Serial Loopback: Routes signals between the transmitter and the receiver.

- VOD: Specifies the voltage output differential of the transmitter buffer.

- Pre-emphasis tap:

- 1st pre: Specifies the amount of pre-emphasis on the pre-tap of the transmitter buffer.

- 1st post: Specifies the amount of pre-emphasis on the first post tap of the transmitter buffer.

- Equalizer: Specifies the CLTE EQ Gain for the receiver.

- AC Gain: Specifies the CLTE AC Gain for the receiver.

- VGA: Specifies the VGA gain value.

All PMA settings should be changed as given in the figure below:

Data Type

Specifies the type of data contained in the transactions. The following data types are available for analysis:

- PRBS 7: Selects pseudo-random 7-bit sequences.

- PRBS 15: Selects pseudo-random 15-bit sequences.

- PRBS 23: Selects pseudo-random 23-bit sequences.

- PRBS 31: Selects pseudo-random 31-bit sequences.

- HF: Selects highest frequency divide-by-2 data pattern 10101010.

- LF: Selects lowest frequency divide-by-33 data pattern.

Error Control

Displays data errors detected during analysis and allows you to insert errors:

- Detected errors: Displays the number of data errors detected in the hardware.

- Inserted errors: Displays the number of errors inserted into the transmit data stream.

- Insert error: Inserts a one-word error into the transmit data stream each time you click the button. Insert error is only enabled during transaction performance analysis.

- Clear: Resets the detected errors and inserted errors counters to zeroes.

Loopback

- Start: Initiates the selected port's transaction performance analysis. Always click Clear before Start.

- Stop: Terminates transaction performance analysis.

- TX and RX performance bars: Show the percentage of maximum theoretical data rate that the requested transactions are able to achieve.