Visible to Intel only — GUID: mwh1409960620169

Ixiasoft

Answers to Top FAQs

1. Introduction to Quartus® Prime Pro Edition

2. Quick Start Steps

3. Planning FPGA Design for RTL Flow

4. Working With Intel® FPGA IP Cores

5. Creating a New FPGA Design Project

6. Migrate Your FPGA Design Project

7. Managing Quartus® Prime Projects

8. Next Steps After Getting Started

A. Using the Design Space Explorer II

B. Document Revision History for Quartus® Prime Pro Edition User Guide Getting Started

4.1. IP Catalog and Parameter Editor

4.2. Installing and Licensing Intel® FPGA IP Cores

4.3. IP General Settings

4.4. Adding IP to IP Catalog

4.5. Best Practices for Intel® FPGA IP

4.6. Specifying the IP Parameters and Options ( Quartus® Prime Pro Edition)

4.7. IP Core Generation Output ( Quartus® Prime Pro Edition)

4.8. Scripting IP Core Generation

4.9. Modifying an IP Variation

4.10. Upgrading IP Cores

4.11. Simulating Intel® FPGA IP Cores

4.12. Generating Simulation Files for Platform Designer Systems and IP Variants

4.13. Synthesizing IP Cores in Other EDA Tools

4.14. Instantiating IP Cores in HDL

4.15. Support for the IEEE 1735 Encryption Standard

4.16. Related Trainings and Resources

6.1.2.1. Modifying Entity Name Assignments

6.1.2.2. Resolving Timing Constraint Entity Names

6.1.2.3. Verifying Generated Node Name Assignments

6.1.2.4. Replace Logic Lock (Standard) Regions

6.1.2.5. Modifying Signal Tap Logic Analyzer Files

6.1.2.6. Removing References to .qip Files

6.1.2.7. Removing Unsupported Feature Assignments

6.1.4.1. Verifying Verilog Compilation Unit

6.1.4.2. Updating Entity Auto-Discovery

6.1.4.3. Ensuring Distinct VHDL Namespace for Each Library

6.1.4.4. Removing Unsupported Parameter Passing

6.1.4.5. Removing Unsized Constant from WYSIWYG Instantiation

6.1.4.6. Removing Non-Standard Pragmas

6.1.4.7. Declaring Objects Before Initial Values

6.1.4.8. Confining SystemVerilog Features to SystemVerilog Files

6.1.4.9. Avoiding Assignment Mixing in Always Blocks

6.1.4.10. Avoiding Unconnected, Non-Existent Ports

6.1.4.11. Avoiding Invalid Parameter Ranges

6.1.4.12. Updating Verilog HDL and VHDL Type Mapping

6.1.4.13. Converting Symbolic BDF Files to Acceptable File Formats

7.1. Viewing Basic Project Information

7.2. Managing Project Settings

7.3. Viewing Parameter Settings From the Project Navigator

7.4. Managing Logic Design Files

7.5. Managing Timing Constraints

7.6. Integrating Other EDA Tools

7.7. Exporting Compilation Results

7.8. Archiving Projects

7.9. Command-Line Interface

7.10. Related Trainings

7.7.1. Exporting a Version-Compatible Compilation Database

7.7.2. Importing a Version-Compatible Compilation Database

7.7.3. Creating a Design Partition

7.7.4. Exporting a Design Partition

7.7.5. Reusing a Design Partition

7.7.6. Viewing Quartus Database File Information

7.7.7. Clearing Compilation Results

Visible to Intel only — GUID: mwh1409960620169

Ixiasoft

4.11.1. Generating IP Simulation Files

The Quartus® Prime software optionally generates the functional simulation model, any testbench (or example design), and vendor-specific simulator setup scripts when you generate an IP core.

To specify options for the generation of IP simulation files, follow these steps:

- To specify your supported simulator and options for design simulation file generation, click Assignment > Settings > EDA Tool Settings > Simulation.

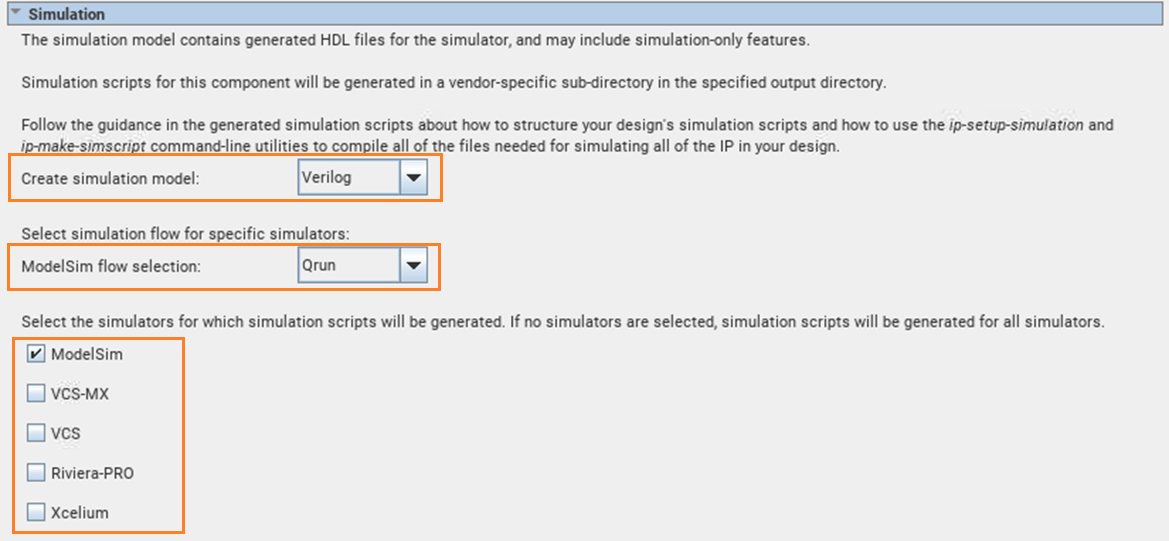

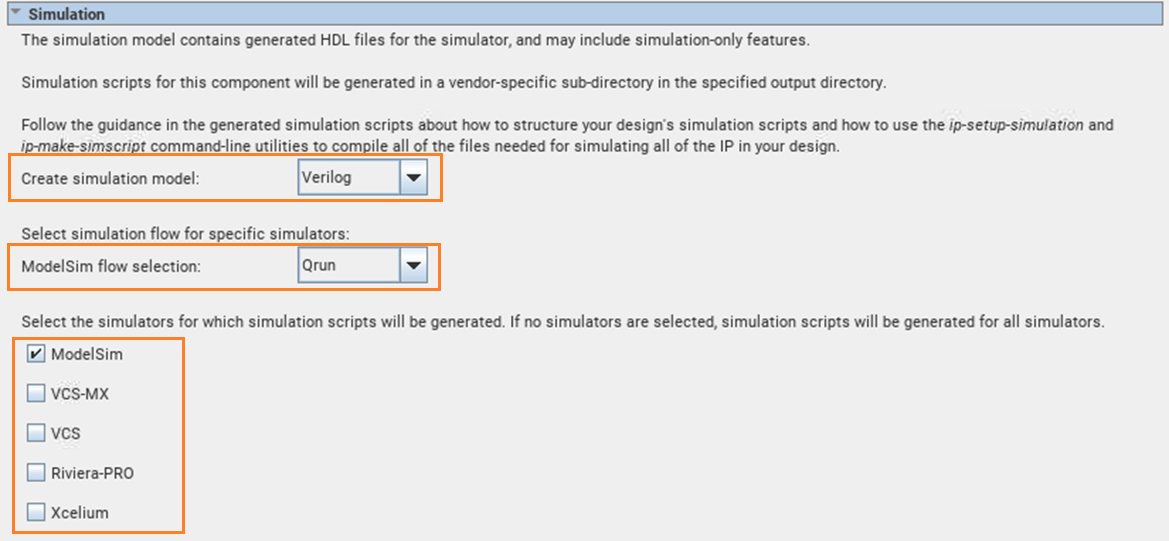

Simulation Options in Generation Dialog Box

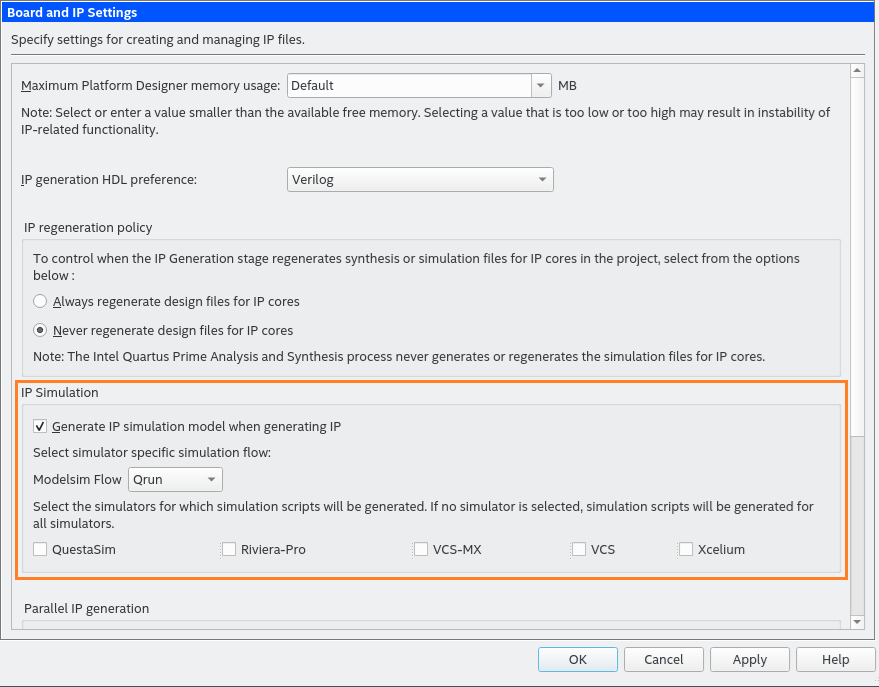

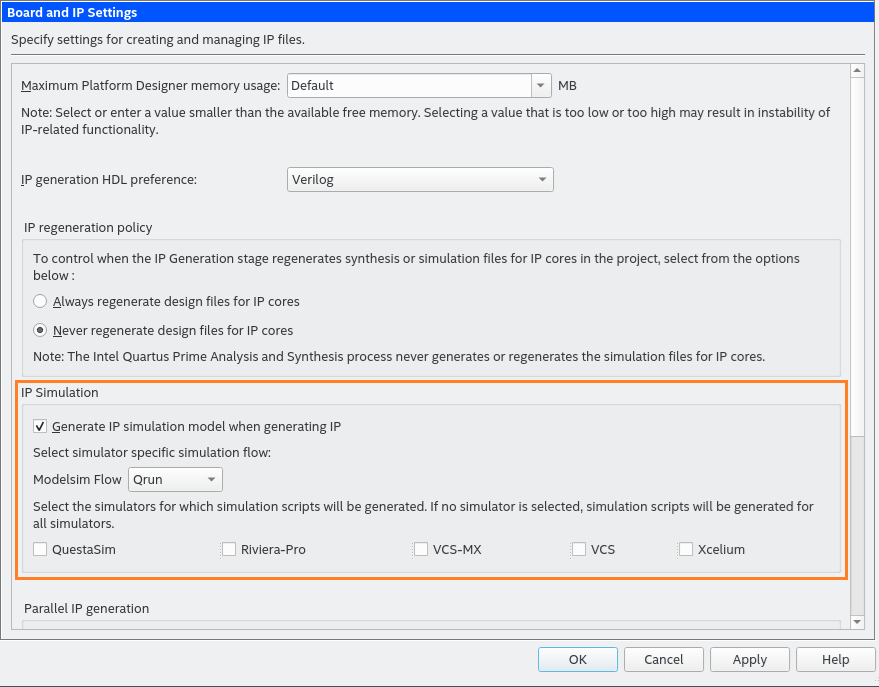

- To specify your supported simulator and options for IP simulation file generation, click Assignments > Settings > Board and IP Settings > IP Simulation and specify the following:

- To enable automatic generation of simulation models for all IP in the project when you generate IP during compilation, turn on the Generate IP simulation model when generating IP option.

- To specify one or more supported simulators for which to generate setup scripts, turn on one or more simulator option, or disable all simulator options to generate scripts for all simulators automatically.

Project-Wide IP Generation Settings

- To generate the simulation files, click Processing > Start Compilation to compile the design. The simulation models and setup scripts for the Intel FPGA IP generate in the <your_project>/<ip name>/sim/<vendor> directory.

You can optionally override these project-level IP Settings when you generate HDL for individual IP cores with the IP Parameter Editor. Prior to generation, you can specify a supported simulator, or specify no simulator to generate the setup scripts for all simulators in the parameter editor.