Visible to Intel only — GUID: hco1423077086281

Ixiasoft

Visible to Intel only — GUID: hco1423077086281

Ixiasoft

13.1.8. Interpolating CIC

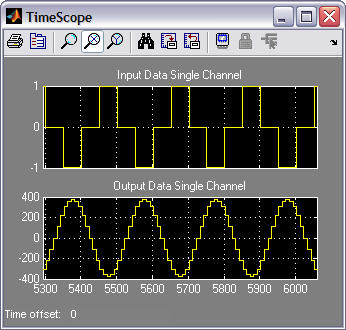

You can use the InterpolatingCIC block in a digital up converter for a radio system or a general purpose DSP application. The coefficients and input data are fixed-point types, and the output is the implied full precision fixed-point type. You can reduce the precision by using a separate Scale block, which can perform rounding and saturation to provide the required output precision.

The InterpolatingCIC block supports rate changes from two upwards.

The InterpolatingCIC has a higher output sample rate than the input sample rate by a factor I, where I is the interpolation rate. Usually, the InterpolatingCIC inserts (I–1) zeros for every input sample, thus raising the sample rate by a factor I.

| Parameter | Description |

|---|---|

| Input rate per channel | Specifies the sampling frequency of the input data per channel measured in millions of samples per second (MSPS). |

| Number of channels | Specifies the number of unique channels to process. |

| Number of stages | Specifies the number of comb and integrator stages. |

| Interpolation factor | Specifies the interpolation factor. Must be an integer. |

| Differential delay | Specifies the differential delay. |

| Final decimation | You can optionally specify a final decimation by 2 to allow interpolation rates which are multiples of 0.5. The decimation works by simply throwing away data values. Only use this option to reduce the number of unique outputs the CIC generates. |

| Signal | Direction | Description |

|---|---|---|

| a | Input | The fixed-point data input to the block. If you request more channels than can fit on a single bus, this signal is a vector. The width in bits is inherited from the input wire. |

| v | Input | Indicates validity of the data input signals. If v is high, the data on the a wire is valid. |

| c | Input | Indicates the channel of the data input signals. If v is high, c indicates which channel the data corresponds to. |

| bypass | Input | When this input is asserted, the input data is zero-stuffed and scaled by the gain of the filter. This option can be useful during hardware debug. |

| q | Output | The fixed-point filtered data output from the block. If you request more channels than can fit on a single bus, this signal is a vector. The width in bits is a function of the input width in bits and the parameterization. |

| v | Output | Indicates validity of data output signals. The output data can be non-zero when v is low. |

| c | Output | Indicates the channel of the data output signals. The output data can be non-zero when v is low. |