Video and Vision Processing Suite Intel® FPGA IP User Guide

A newer version of this document is available. Customers should click here to go to the newest version.

Visible to Intel only — GUID: axc1683281645791

Ixiasoft

Visible to Intel only — GUID: axc1683281645791

Ixiasoft

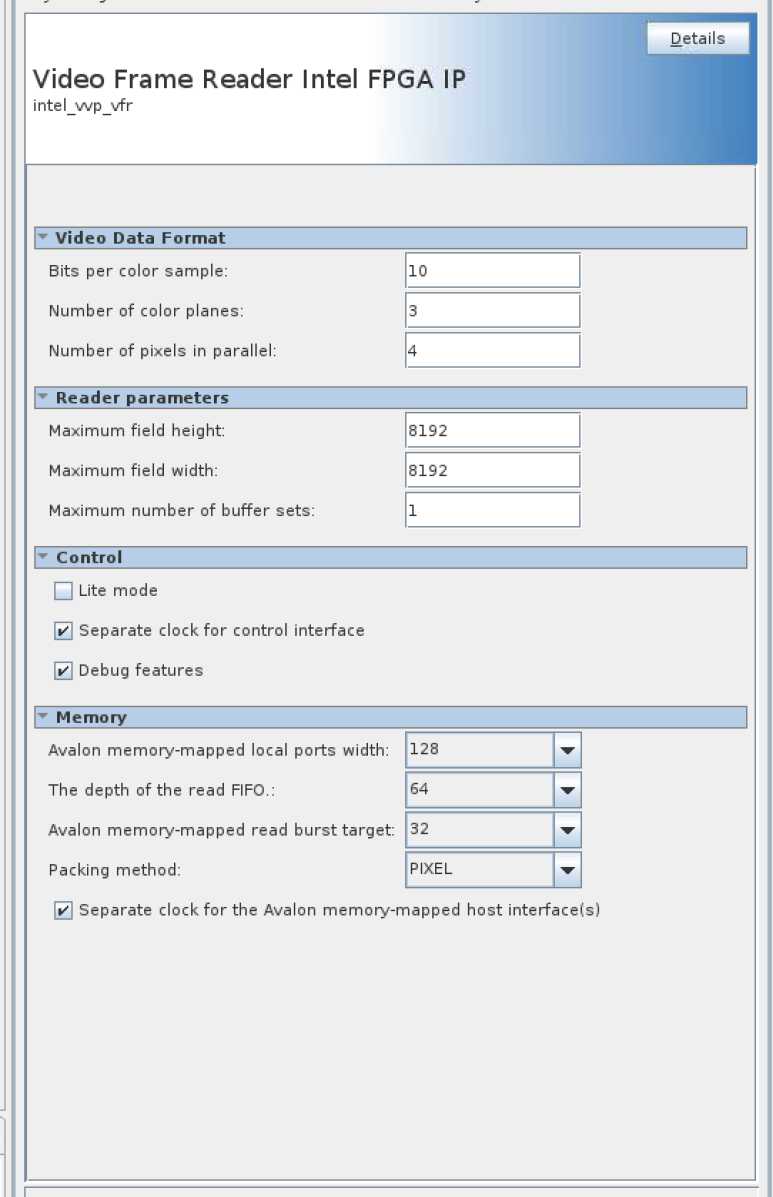

45.2. Video Frame Reader IP Parameters

| Parameter | Values | Description |

|---|---|---|

| Video Data Format | ||

| Bits per color sample | 8 to 16 | Select the number of bits per color sample. |

| Number of color planes | 1 to 4 | Select the number of color planes per pixel. |

| Number of pixels in parallel | 1 to 8 | Select the number of pixels in parallel. |

| Maximum Frame Size | ||

| Maximum frame height | 32 to 16384 | Select the maximum height of frames. If you attempt to read out fields or frames taller than this value, the IP crops them to this height. |

| Maximum frame width | 32 to 16384 | Select the maximum width of frames. If you attempt to read out fields or frames wider than this value, the IP crops them to this width. If you use the IP exclusively to read frames with 420 subsampling, optionally halve the maximum frame width entry in the GUI. Halving the entry optimizes memory footprint because of the more efficient 420 pixel packing. |

| Maximum number of buffer sets | 1 to 16 | Select the maximum number of buffer sets. Each buffer set implements a set of 16 additional control registers. To save resources configure the maximum number of buffer sets required for your application and no more. Most applications only require 1 or 2 buffer sets. |

| Control | ||

| Lite mode | On or off | Turn on to operate the frame reader in lite mode. |