Visible to Intel only — GUID: gly1482303505490

Ixiasoft

Visible to Intel only — GUID: gly1482303505490

Ixiasoft

Building the Base Revision with the Reconfigurable Design Partition

- Run the first two stages of the compilation flow (IP Generation and Analysis & Synthesis). This generates the design hierarchy so that the reconfigurable design partition and LogicLock Plus assignments can be added.

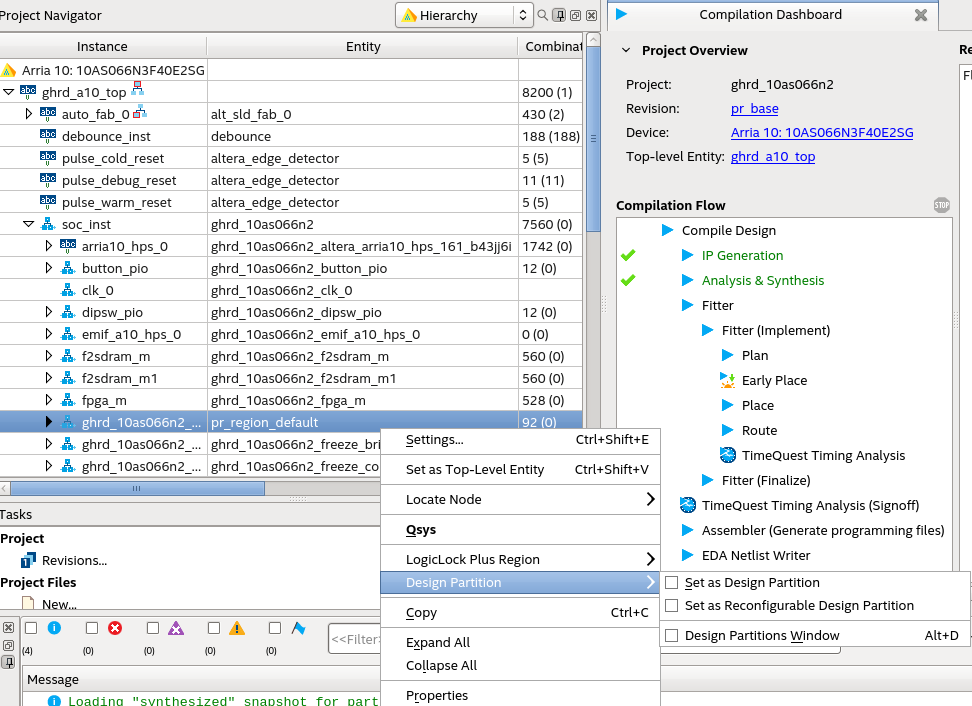

- To create a reconfigurable design partition, right-click the design instance of the PR region, point to Design Partition, and click Set as Reconfigurable Design Partition as shown below.

Figure 24. Creating a Reconfigurable Design Partition

- To create a new LogicLock Plus region, similarly right-click the design instance, point to LogicLock Plus Region, and click Create New LogicLock Plus Region.

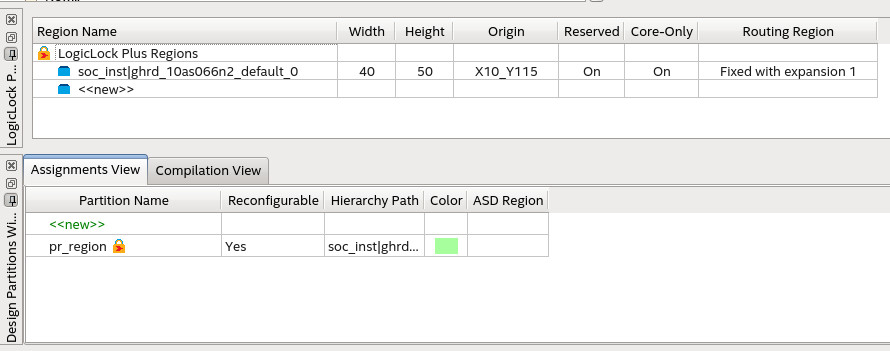

- Set the properties of the design partition and LogicLock Plus region using the editor windows.1 Edit the assignments as shown below. Change the design partition name to something generic, like “pr_region”. Make sure to adjust the LogicLock Plus placement, enable the Reserved and Core-Only attributes, and change the Routing Region type to Fixed with expansion of 1.

For detailed information about design partition settings, refer to "Create Design Partitions for Partial Reconfiguration" in the Creating a Partial Reconfiguration Design chapter of the Quartus Prime Pro Edition Handbook Volume 1: Design and Compilation.Figure 25. Configure Partition and Region Properties

- Run a full compilation flow as follows:

- If the Compilation Dashboard is not visible, click Compilation Dashboard in the Tasks window.

- Click Compile Design.

The following critical files are in the output_files/ directory after the compilation flow finishes:

- pr_base.sof

- pr_base.pr_region.pmsf

These files contain the FPGA configuration images for the default complete FPGA and the PR region default persona, respectively. These files are converted to RBF images in a later step.