Visible to Intel only — GUID: ync1715933500117

Ixiasoft

1. Overview

2. Getting Started

3. Development Kit Setup

4. Board Test System

5. Development Kit Hardware and Configuration

6. Custom Projects for the Development Kit

7. HPS Boot

8. Document Revision History for the Agilex™ 5 FPGA E-Series 065B Modular Development Kit User Guide

A. Development Kit Components

B. Additional Information

Visible to Intel only — GUID: ync1715933500117

Ixiasoft

6.2. EMIF Pin Swizzling Setting

DQ pins within a DQS group or/and DQS group are swapped to simplify board design.

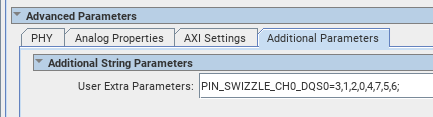

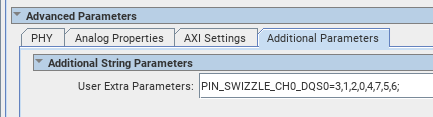

To achieve the swizzling, you must enter swizzling setting in the User Extra Parameters field of the Additional Parameters tab in the Advanced Parameters section of the General IP Parameters tab in the External Memory Interfaces (EMIF) IP parameter editor.

Figure 38. Entering a PIN_SWIZZLE Specification

- For DDR4 Bank 2B, use the following settings:

BYTE_SWIZZLE_CH0=1,X,X,X,0,2,3,X; PIN_SWIZZLE_CH0_DQS0=7,5,1,3,4,2,0,6; PIN_SWIZZLE_CH0_DQS1=9,15,13,11,14,12,8,10; PIN_SWIZZLE_CH0_DQS2=19,23,21,17,16,18,20,22; PIN_SWIZZLE_CH0_DQS3=31,29,27,25,26,30,24,28;

- For DDR4 Bank 3A, use the following settings:

BYTE_SWIZZLE_CH0=0,X,X,X,1,2,3,ECC; PIN_SWIZZLE_CH0_DQS0=2,0,6,4,7,5,3,1; PIN_SWIZZLE_CH0_DQS1=14,11,12,8,10,9,13,15; PIN_SWIZZLE_CH0_DQS2=16,20,22,18,23,21,19,17; PIN_SWIZZLE_CH0_DQS3=26,30,28,24,25,27,29,31; PIN_SWIZZLE_CH0_ECC=4,6,2,0,1,7,5,3;

- For DDR4 Bank 3B, use the below settings:

BYTE_SWIZZLE_CH0=0,X,X,X,1,2,3,ECC; PIN_SWIZZLE_CH0_DQS0=2,0,6,4,7,3,5,1; PIN_SWIZZLE_CH0_DQS1=12,14,13,10,8,11,15,9; PIN_SWIZZLE_CH0_DQS2=16,17,18,19,20,21,22,23; PIN_SWIZZLE_CH0_DQS3=24,25,26,27,28,29,30,31; PIN_SWIZZLE_CH0_ECC=0,2,6,4,1,3,7,5;