Visible to Intel only — GUID: try1719545949425

Ixiasoft

1. About the 1G/2.5G/5G/10G Multirate Ethernet PHY Intel® FPGA IP for Agilex™ 5 Devices

2. Getting Started

3. Functional Description

4. Parameter Settings for 1G/2.5G/5G/10G Multirate Ethernet PHY Intel® FPGA IP

5. Interface Signals

6. Configuration Registers

7. 1G/2.5G/5G/10G Multirate Ethernet PHY Intel® FPGA IP User Guide: Agilex™ 5 FPGAs and SoCs Archives

8. Document Revision History for the 1G/2.5G/5G/10G Multirate Ethernet PHY Intel® FPGA IP User Guide: Agilex™ 5 FPGAs and SoCs

5.1. Clock Signals

5.2. Reset Signals

5.3. Serial Interface Signals

5.4. Avalon Memory-Mapped Interface Signals

5.5. XGMII Signals

5.6. GMII Signals

5.7. PHY Status Signals

5.8. Transceiver Mode and Operating Speed Signals

5.9. Transceiver Status and Reconfiguration Signals

5.10. GTS Reset Sequencer Signals

5.11. Dynamic Reconfiguration SRC Signals

Visible to Intel only — GUID: try1719545949425

Ixiasoft

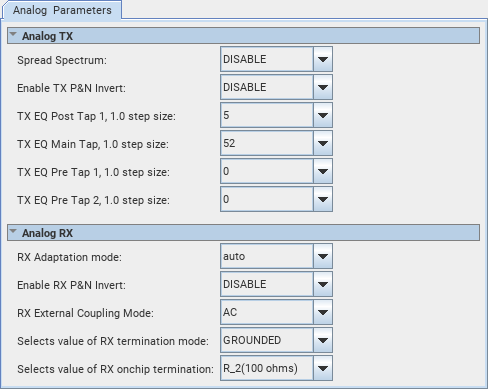

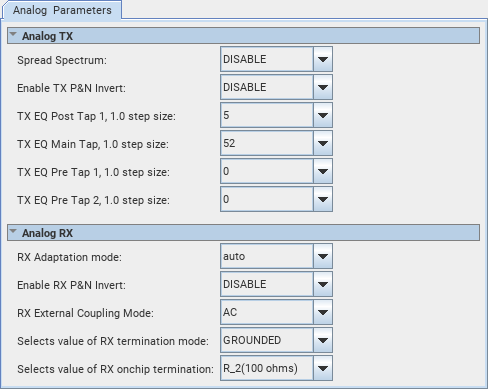

4.2. Analog Parameters

Figure 15. Analog Parameters Tab

For more information on the analog parameter configuration, refer to Configurable Quartus® Prime Software Settings in the GTS Transceiver PHY User Guide.

Related Information