Visible to Intel only — GUID: uik1723713134259

Ixiasoft

Visible to Intel only — GUID: uik1723713134259

Ixiasoft

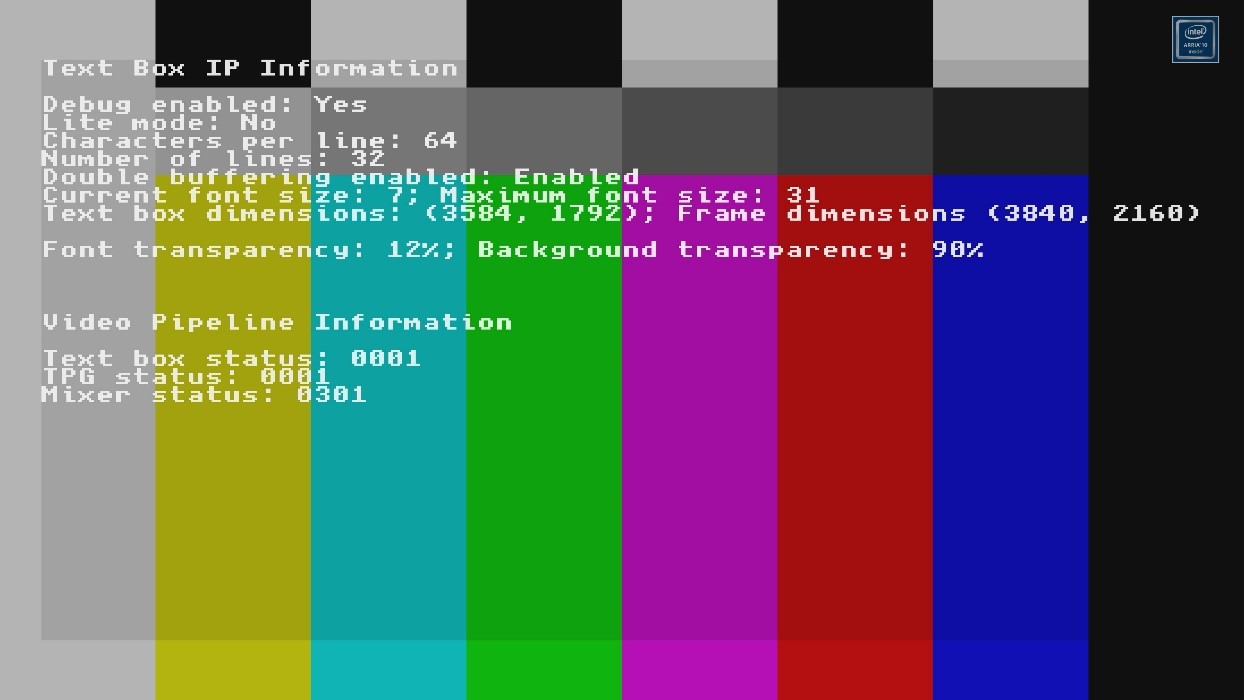

42.3. Text Box IP Functional Description

The number of characters per line and number of lines are fixed at compile-time. However if Memory-mapped control interface is on you can update the font size, font, and background colors and interlace configuration at run time. The field size changes as font size changes, and the field height halves if Fixed interlace nibble is 8 to 15..

| Color Space | Number of color planes | Number of color planes with Enable alpha channel |

|---|---|---|

| RGB | 3 | 4 |

| YCbCr 4:4:4 | 3 | 4 |

| YCbCr 4:2:2 | 2 | 3 |

| YCbCr 4:20 | 3 | 4 |

| Monochrome | 1 | 2 |

Text Box Format

The number of characters per line is: n chars , and number of lines named is n lines . Character index is i.

The IP sequentially indexes each character starting from 0, with maximum index of:

(n chars x n lines )-1

that is:

0≤i ≤(n chars *n lines )-1}

The line or row number is:

i/n chars

The column number is:

i mod n chars

That is, the text wraps to the next line at index n chars .

If Memory-mapped control interface is on, you can write a string by writing the character's ASCII code to the corresponding addresses. The control interface takes 4 bytes of data, where characters are ordered in little-endian (to write the string "0123" (ASCII values 0x30, 0x31, 0x32, 0x33) you write "0x33323130" to address 0x200). You may use the control interface's byte-enable signal to write to specific bytes only.

If Memory-mapped control interface is off, the IP shows static text with the contents of the file in the Text file name parameter. The file automatically is formatted into an initialization file and used as ROM.

Field Dimensions

You select progressive or interlaced outputs with Fixed interlace nibble or in the FIELD_INTERLACE register.

The IP derives the field size from the font size, number of characters per line, and number of lines. Each character is 8x8 pixels with font size of 1. For progressive output:

- The width is (8 x font size x n_ chars )

- The height is (8 x font size x n_ lines )

For interlaced output, the IP halves the field height so that when deinterlacing F0 with F1 the output is identical to a progressive frame.

- The width is (8 x font size x n_ chars )

- The height is (4 x font size x n_ lines )

If Memory-mapped control interface is on, the field size updates whenever the font size or interlace settings change.