Video and Vision Processing Suite Intel® FPGA IP User Guide

A newer version of this document is available. Customers should click here to go to the newest version.

Visible to Intel only — GUID: yvr1723713087664

Ixiasoft

Visible to Intel only — GUID: yvr1723713087664

Ixiasoft

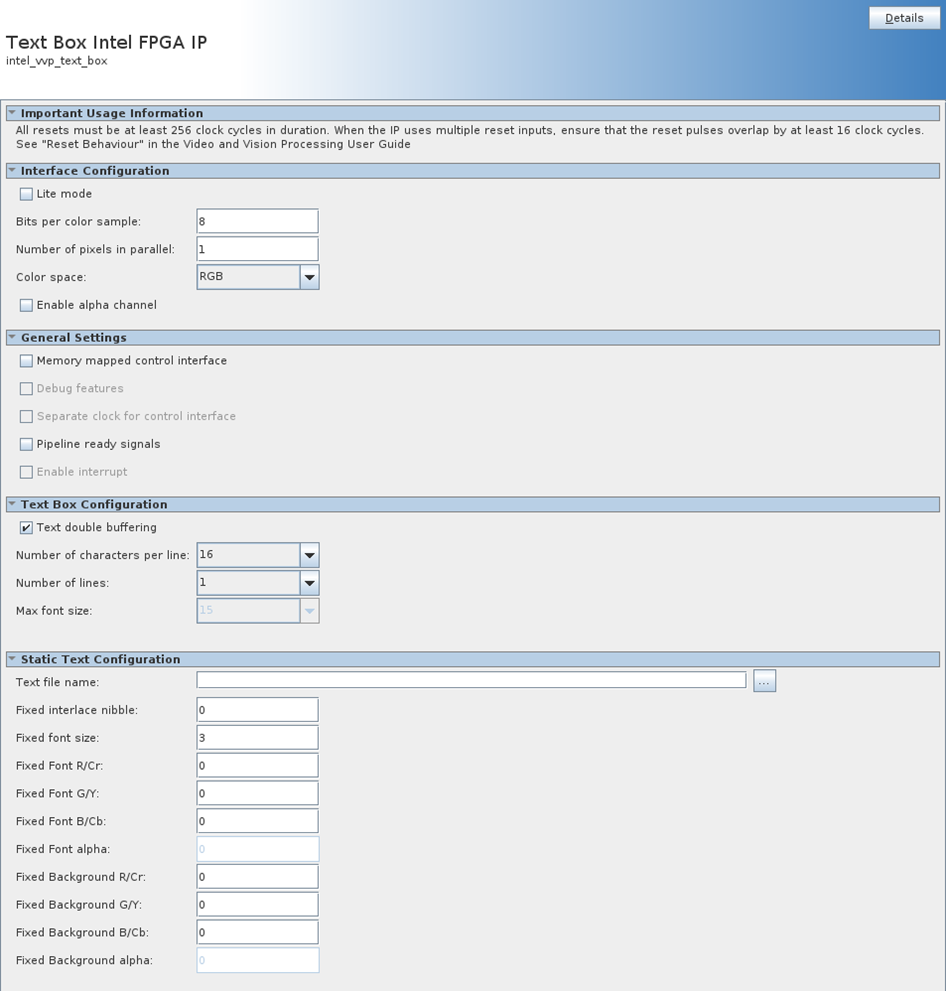

42.2. Text Box IP Parameters

| Parameter | Values | Description |

|---|---|---|

| Interface Configuration | ||

| Lite mode | On or Off | Turn on to use the Lite variant of the Intel FPGA Streaming Video Protocol |

| Bits per color sample | 8 to 16 | Select the number of bits per color sample |

| Number of pixels in parallel | 1 to 8 | Select the number of pixels transmitted per clock cycle |

| Color space | RGB, YCbCr 4:4:4, YCbCr 4:2:2, YCbCr 4:2:0, Monochrome | Select the output color space. RGB, YCbCr 4:4:4 and YCbCr 4:2:0 have 3 color channels. YCbCr 4:2:2 has 2 color channels. Monochrome has 1 color channel. |

| Enable alpha channel | On or Off | Turn on to add an extra alpha color plane containing transparency information |

| General Settings | ||

| Memory mapped control interface | On or Off | Turn on for the Memory-mapped control interface and allow runtime configuration of the IP via the register map. |

| Debug features | On or Off | Turn on for read back of writable registers via the Memory-mapped control interface. If off, you cannot read back from any writable registers. Read-only registers are always readable. |

| Separate clock for control interface | On or Off | Turn on for a separate clock for the Memory mapped control interface. |

| Pipeline ready signals | On or Off | Enable to add extra pipeline registers to AXI4-S tready signals |

| Enable interrupt |

On or Off | 129 Add an interrupt sender signal that fires when the IP accepts configuration for the next frame, indicating when it is safe to start writing new settings. |

| Text Box Configuration | ||

| Text double buffering | On or Off | 129 Turn on to add a second text buffer, allowing you to control both which buffer you write text to, and which buffer the IP uses. |

| Number of characters per line | 1, 2, 4, 8, 16, 32, 64, 128, 256 | The number of characters you can write per line of text. The field/frame width is derived from this parameter and the Maximum font size. |

| Number of lines | 1, 2, 4, 8, 16, 32, 64, 128, 256 | The number of lines of text. The IP derives the field or frame height from this parameter and the Maximum font size. |

| Maximum font size | 3, 7, 15, 31, 63, 127, 255 | 129 Set the maximum font size available to be set at runtime. This parameter with Number of characters per line and Number of lines determine the maximum field dimensions. With a font size of 1, each character is 8x8 pixels |

| Static Text Configuration | ||

| Text file name | A valid filepath | 130 Select the text file that contains the static text to display. The text is truncated horizontally if a line is longer than Number of characters per line, and truncated vertically if the file is longer than Number of lines. |

| Fixed interlace nibble | 0 to 15 | 130 Select the required initial interlace nibble configuration, as described by the Intel FPGA Streaming Video protocol.

If Lite mode is off, this value populates the initial image information packet. |

| Fixed font size | 3 to 255 | 130 Set the font size for the static text. The fixed field width is (Number of characters per line * Fixed font size * 8) The fixed field height is (Number of lines * Fixed font size * 8) |

| Fixed font color (R/Cr) | 0 to (2 bits per color sample) - 1 | 130 Set the static text’s font color R component if color space is RGB, or Cr if color space is YCbCr. |

| Fixed font color (G/Y) | 0 to (2 bits per color sample) - 1 | 130 Set the static text’s font color G component if color space is RGB, or Y if color space is YCbCr. |

| Fixed font color (B/Cb) | 0 to (2 bits per color sample) - 1 | 130 Set the static text’s font color B component if color space is RGB, or Cb if color space is YCbCr, or the monochrome component. |

| Fixed font alpha | 0 to (2 bits per color sample) - 1 | Only if Memory-mapped control interface is off and Enable alpha channel is on. Set the static text’s font alpha value. |

| Fixed background color (R/Cr) | 0 to (2 bits per color sample) - 1 | 130 Set the static text’s background color R component if color space is RGB, or Cr if color space is YCbCr. |

| Fixed background color (G/Y) | 0 to (2 bits per color sample) - 1 | 130 Set the static text’s background color G component if color space is RGB, or Y if color space is YCbCr. |

| Fixed background color (B/Cb) | 0 to (2 bits per color sample) - 1 | 130 Set the static text’s background color B component if color space is RGB, or Cb if color space is YCbCr, or the monochrome component. |

| Fixed background alpha | 0 to (2 bits per color sample) - 1 | Only if Memory-mapped control interface is off, and Enable alpha channel is on. Set the static text’s background alpha value. |