Intel Acceleration Stack for Intel® Xeon® CPU with FPGAs Core Cache Interface (CCI-P) Reference Manual

Visible to Intel only — GUID: jrj1506278530260

Ixiasoft

Visible to Intel only — GUID: jrj1506278530260

Ixiasoft

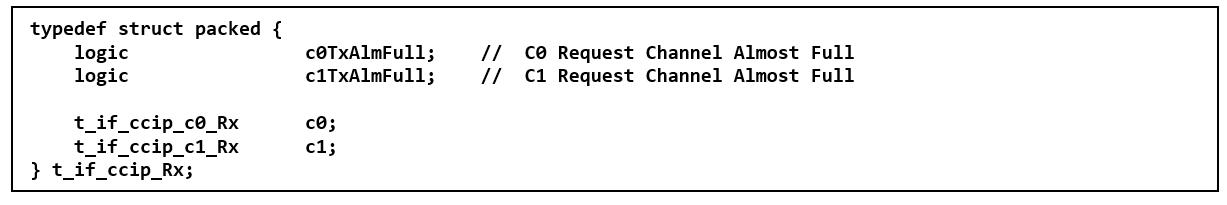

1.3.8. CCI-P Rx Signals

There are two Rx channels:

- Channel 0 interleaves memory responses, MMIO requests and UMsgs.

- Channel 1 returns responses for AFU requests initiated on Tx Channel 1.

The c0TxAlmFull and c1TxAlmFull signals are inputs to the AFU. Although they are declared with the Rx signals structure, they logically belong to the Tx interface and so were described in the previous section.

Rx Channels have no flow control. The AFU must accept responses for memory requests it generated. The AFU must pre-allocate buffers before generating a memory request. The AFU must also accept MMIO requests.

Rx Channel 0 has separate valid signals for memory responses and MMIO requests. Only one of those valid signals can be set in a cycle. The MMIO request has a separate valid signal for MMIO Read and MMIO Write. When either mmioRdValid or mmioWrValid is set, the message is an MMIO request and should be processed by casting t_if_ccip_c0_Rx.hdr to t_ccip_c0_ReqMmioHdr.

| Signal | Width (bits) | Direction | Description |

|---|---|---|---|

| pck_cp2af_sRx.c0.hdr | 28 | Input | Channel 0 response header or MMIO request header. Refer to Table 21. |

| pck_cp2af_sRx.c0.data | 512 | Input | Channel 0 Data bus Memory Read Response and UMsg:

MMIO Write Request:

|

| pck_cp2af_sRx.c0.rspValid | 1 | Input | When set to 1, it indicates header and data on Channel 0 are valid. The header must be interpreted as a memory response, decode resp_type field. |

| pck_cp2af_sRx.c0.mmioRdValid | 1 | Input | When set to 1, it indicates a MMIO Read request Channel 0. |

| pck_cp2af_sRx.c0.mmioWrValid | 1 | Input | When set to 1, it indicates a MMIO Write request on Channel 0. |

| Signal | Width (bits) | Direction | Description |

|---|---|---|---|

| pck_cp2af_sRx.c1.hdr | 28 | Input | Channel 1 response header. Refer to Table 21 |

| pck_cp2af_sRx.c1.rspValid | 1 | Input | When set to 1, it indicates header on channel 1 is a valid response. |