Visible to Intel only — GUID: qzk1506351718681

Ixiasoft

Visible to Intel only — GUID: qzk1506351718681

Ixiasoft

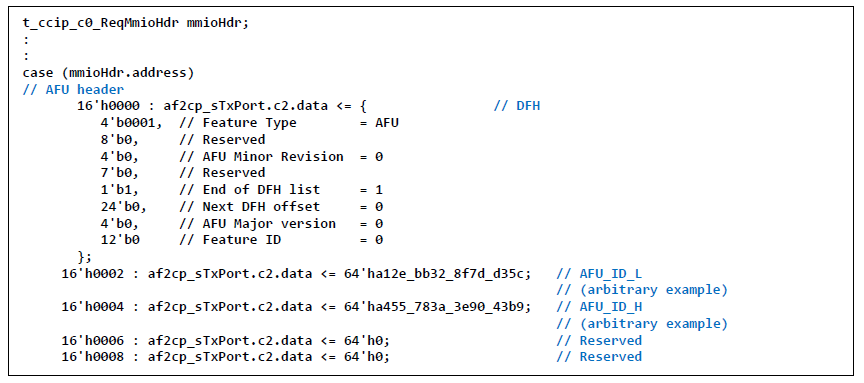

1.4.1. Mandatory AFU CSR Definitions

The following requirements are defined for software access to AFU CSRs.

- Software is expected to access 64-bit CSRs as aligned quad words (8 bytes). To modify a field (for example, bit or byte) in a 64-bit register, the entire quad word is read, the appropriate field(s) are modified, and the entire quad word is written back (read-modify-write operation).

- Similarly for an AFU supporting 32-bit CSRs, software is expected to access them as aligned double words (4 bytes).

Each CCI-P-compliant AFU is required to implement the four (not including DEV_FEATURE_HDR (DFH) at 0x0000) mandatory registers defined in the table below. If you do not implement these registers or if you implement them incorrectly, AFU discovery could fail or some other unexpected behavior may occur.

| Attribute | Expansion | Description |

|---|---|---|

| RO | Read Only | The bit is set by hardware only. Software can only read this bit. Writes do not have any effect. |

| Rsvd | Reserved | Reserved for future definition. AFU must set them to 0s. Software must ignore these fields. |

| Name | DWORD Address Offset (CCI-P) |

Byte Address Offset (Software) |

|---|---|---|

| DEV_FEATURE_HDR (DFH)

For bit descriptions, refer to Table 43.

Note: AFU CSRs are 64 bits.

|

0x0000 | 0x0000 |

| AFU_ID_L Lower 64 bits of the AFU_ID GUID. |

0x0002 | 0x0008 |

| AFU_ID_H Upper 64 bits of the AFU_ID GUID. |

0x0004 | 0x0010 |

| DFH_RSVD0 | 0x0006 | 0x0018 |

| DFH_RSVD1 | 0x0008 | 0x0020 |

The software and the AFU RTL must reference the same AFU ID.

| Bit | Attribute | Default | Description |

|---|---|---|---|

| 63:60 | RO | 0x1 | Type: AFU |

| 59:52 | Rsvd | 0x0 | Reserved |

| 51:48 | RO | 0x0 | AFU Minor version number User defined value |

| 47:41 | Rsvd | 0x0 | Reserved |

| 40 | RO | N/A | End of List 1’b0: There is another feature header beyond this (see “Next DFH Byte Offset”) 1’b1: This is the last feature header for this AFU |

| 39:16 | RO | 0x0 | Byte offset to the Next Device Feature Header; that is, offset from the current address. For an example of DFH byte offset, refer to Table 45. |

| 15:12 | RO | 0x0 | AFU Major version number User defined value |

| 11:0 | RO | N/A | CCI-P version number Use the CCIP_VERSION_NUMBER parameter from ccip_if_pkg.sv |