Visible to Intel only — GUID: gum1638455393095

Ixiasoft

Visible to Intel only — GUID: gum1638455393095

Ixiasoft

4.5.2.2. SDM Bootloader Example Design

You can generate the SDM Bootloader Example Design from the IP Catalog. The example design is based on the Intel Stratix 10 SX SoC L-Tile development kit. Using the provided scripts, the hardware and software design are generated, and programmed respectively as SRAM Object Files (.sof) and JTAG Indirect Configuration Files (.jic) into the device.

For more information about booting the Nios V processor-based system from SDM based FPGA devices, refer to Nios V Processor Application Copied from Configuration QSPI Flash to RAM Using Boot Copier (SDM Bootloader)

To generate the SDM Bootloader Example Design using Platform Designer,

- In the Intel® Quartus® Prime software, go to Tools > Platform Designer.

- In the Platform Designer, select IP Variant.

- For Quartus project, select None.

- In the IP Variant dialog box, specify any name for your IP.

Note: Saving the IP is not required.

- Click Select in the Component type.

- The IP Catalog opens.

- Search for Nios V/m Processor Intel FPGA IP.

- Create the IP design.

Figure 69. IP Parameter Editor for Nios® V/m Processor Intel® FPGA IP - Click Example Design: “SDM Bootloader Example Design and select your project folder.

- Close the IP Parameter Editor. When prompted with Save changes?, you do not need to save the IP. Click Don’t Save.

- Unzip the example design to your project folder. Refer to table below for the example design files and the description.

To generate the SDM Bootloader Example Design using CLI,

<Intel Quartus Prime installation directory>/niosv/bin/niosv-shellNote: Disregard this command if you are already using Nios V command Shell.ip-deploy --component-name=intel_niosv_m --output-name=niosv_m.ipqsys-generate niosv_m.ip \ --example_design=niosv_m.sdm_bootloader_example_designunzip s10soc_niosv_m_sdm_bootloader_example_design.zip

| File | Description |

|---|---|

| software/mailbox_bootloader/app | Folder containing source code for SDM bootloader. |

| software/user_application/app | Folder containing source code for user application. |

| create_design.py | Python script to build the example design and program the device. |

| flash_settings.pfg | Provide information to generate the JIC file using Programming File Generator tool. |

| mailbox_bootloader_bsp_script.tcl | TCL script to configure the BSP Editor for SDM bootloader. |

| qsys_system_script.tcl | TCL script to generate the example design .qsys file. |

| readme.txt | Description and steps to build the example design. |

| toggle_issp.tcl | TCL script to reset the design via In-System Sources and Probes (ISSP). |

| top.sdc | Example design Synopsys* Design Constraints (.sdc) file. |

| top.tcl | TCL script to generate the example design .qpf file and .qsf file. |

| top.v | Top-level Verilog design. |

| user_application_bsp_script.tcl | TCL script to configure the BSP Editor for user application. |

Running the SDM Bootloader Example Design

- Launch the Nios V Command Shell.

- Run create_design.py to build the example design and program the Intel Stratix 10 SX SoC L-Tile development kit.

quartus_py create_design.py

- Reset the Nios V processor.

quartus_stp -t toggle_issp.tcl

- Run JUART terminal to view the outputs.

juart-terminal

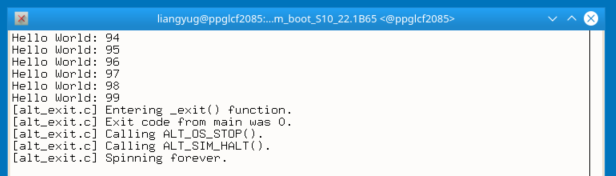

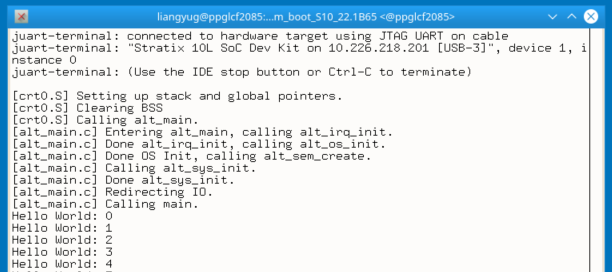

Figure 70. SDM Bootloader Example Design

- In the beginning, the window displays the following message

- Reaching the end, the window displays the following message: