Visible to Intel only — GUID: vgg1675204485868

Ixiasoft

1. About the F-Tile Dynamic Reconfiguration Suite Intel® FPGA IP Core

2. Interface Overview

3. Parameters

4. Designing with the IP Core

5. Block Description

6. Configuration Registers

7. F-Tile Dynamic Reconfiguration Suite Intel® FPGA IP User Guide Archives

8. Document Revision History for F-Tile Dynamic Reconfiguration Suite Intel® FPGA IP User Guide

4.1. Generating Dynamic Reconfiguration Design and Configuration Profiles

4.2. Dynamic Reconfiguration QSF Settings

4.3. Dynamic Reconfiguration Using QSF-driven Flow

4.4. Dynamic Reconfiguration Rules

4.5. Hardware States and Configuration Profiles

4.6. Nios® -Based Dynamic Reconfiguration Flow

4.7. Using the Tile Assignment Editor

4.8. Visualizing Dynamic Reconfiguration Group Placement

4.9. Assigning IP_COLOCATE Hierarchy

4.10. Example: Dynamic Reconfiguration with Multirate IP Flow

4.11. Example: Dynamic Reconfiguration Programming Sequence

4.12. Dynamic Reconfiguration Error Recovery Handling

4.13. Determining Profile Numbers

4.14. Master Clock Channel

4.15. Using the IP_RECONFIG_GROUP_PARENT QSF Assignment

6.1. Dynamic Reconfiguration New Trigger

6.2. Dynamic Reconfiguration Next Profile 0

6.3. Dynamic Reconfiguration Next Profile 1

6.4. Dynamic Reconfiguration Next Profile 2

6.5. Dynamic Reconfiguration Next Profile 3

6.6. Dynamic Reconfiguration Next Profile 4

6.7. Dynamic Reconfiguration Next Profile 5

6.8. Dynamic Reconfiguration Next Profile 6

6.9. Dynamic Reconfiguration Next Profile 7

6.10. Dynamic Reconfiguration Next Profile 8

6.11. Dynamic Reconfiguration Next Profile 9

6.12. Dynamic Reconfiguration Next Profile 10

6.13. Dynamic Reconfiguration Next Profile 11

6.14. Dynamic Reconfiguration Next Profile 12

6.15. Dynamic Reconfiguration Next Profile 13

6.16. Dynamic Reconfiguration Next Profile 14

6.17. Dynamic Reconfiguration Next Profile 15

6.18. Dynamic Reconfiguration Next Profile 16

6.19. Dynamic Reconfiguration Next Profile 17

6.20. Dynamic Reconfiguration Next Profile 18

6.21. Dynamic Reconfiguration Next Profile 19

6.22. Dynamic Reconfiguration Avalon MM Timeout

6.23. Dynamic Reconfiguration TX Channel Reconfiguration

6.24. Dynamic Reconfiguration RX Channel Reconfiguration

6.25. Dynamic Reconfiguration TX Channel in Reset Acknowledgment

6.26. Dynamic Reconfiguration TX Channel out of Reset

6.27. Dynamic Reconfiguration TX Channel Reset Control Init Status

6.28. Dynamic Reconfiguration TX Channel Source Alarm

6.29. Dynamic Reconfiguration RX Channel in Reset Acknowledgment

6.30. Dynamic Reconfiguration RX Channel out of Reset

6.31. Dynamic Reconfiguration RX Channel Reset Control Init Status

6.32. Dynamic Reconfiguration RX Channel Source Alarm

6.33. Dynamic Reconfiguration Local Error Status

Visible to Intel only — GUID: vgg1675204485868

Ixiasoft

4.14.2. Automation for selecting the Master Clock Channel

This section describes a method which allows the Intel Quartus Prime software to automatically select the System PLL DIV2 output for dynamic reconfiguration of the protocol IP. Using this method alleviates the need to specify a stable, non-reconfigurable master clock channel within the protocol IP.

In order to allow the Intel Quartus Prime software to automatically select the system PLL DIV2 output for dynamic reconfiguration protocol IP, perform the following steps:

- Configure the protocol IP instance with the targeted settings.

- Create your RTL design. There are no special connections required in the RTL for this method.

- In Quartus, run the Support-Logic Generation.

- Open Tile Assignment Editor.

- Create a new Dynamic Reconfiguration group.

- Add your protocol IP instance to the Reconfiguration group.

- Assign the proper Reconfiguration Controller to the Reconfiguration Group.

- Click on the Has master clock channel check box.

- Do NOT assign a Master Clock Channel.

Leave Use master clock channel from field blank.

- Click on Save Tile Alignment Editor button.

- Compile the dynamic reconfiguration design.

For example, consider an example design that includes three instances of Direct PHY Multirate IP variants spread across two tiles.

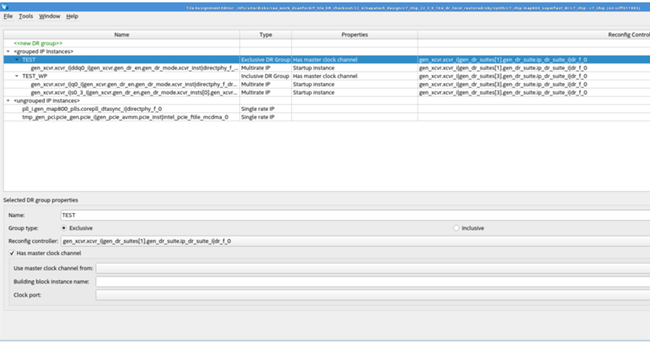

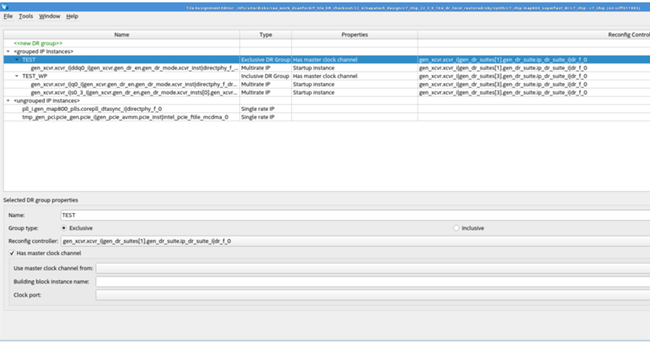

Figure 23. Tile Assignment Editor includes three instances of Direct PHY Multirate IP variants spread across two tiles.

In the above screenshot, the following reconfiguration groups are created:

- Test

- Test_WP

Quartus uses this information to automatically select the System PLL DIV2 source for dynamic reconfiguration, eliminating the need to reserve a stable PMA stream for the master clock channel.

The QSF assignments which are generated from the above Tile Assignment Editor are shown below:

set instance_assignmsetent -name IP_COLOCATE F_TILE -from

gen_xcvr.xcvr_i|gen_dr_suites[3].gen_dr_suite.ip_dr_suite_i|dr_f_0 -to

gen_xcvr.xcvr_i|s0_3_i|gen_xcvr.gen_dr_en.gen_dr_mode.xcvr_insts[0].gen_xcvr_en.xcvr_inst|directphy_f_dr_0 -entity c7_chip

set_instance_assignment -name IP_COLOCATE F_TILE -from

gen_xcvr.xcvr_i|gen_dr_suites[3].gen_dr_suite.ip_dr_suite_i|dr_f_0 -to

gen_xcvr.xcvr_i|q0_i|gen_xcvr.gen_dr_en.gen_dr_mode.xcvr_inst|directphy_f_dr_0 -entity c7_chip

set_instance_assignment -name IP_COLOCATE F_TILE -from

gen_xcvr.xcvr_i|gen_dr_suites[1].gen_dr_suite.ip_dr_suite_i|dr_f_0 -to

gen_xcvr.xcvr_i|ddq0_i|gen_xcvr.gen_dr_en.gen_dr_mode.xcvr_inst|directphy_f_dr_0 -entity c7_chip

set_global_assignment -name IP_RECONFIG_GROUP_TYPE "TEST:EXCLUSIVE:CLK_MASTER" -entity c7_chip

set_global_assignment -name IP_RECONFIG_GROUP_TYPE "TEST_WP:INCLUSIVE:CLK_MASTER" -entity c7_chip

set_instance_assignment -name IP_RECONFIG_GROUP_MASTER_CLOCK_CHANNEL OFF -to

gen_xcvr.xcvr_i|ddq0_i|gen_xcvr.gen_dr_en.gen_dr_mode.xcvr_inst|directphy_f_dr_0 -entity c7_chip

set_instance_assignment -name IP_RECONFIG_GROUP_MASTER_CLOCK_CHANNEL OFF -to

gen_xcvr.xcvr_i|s0_3_i|gen_xcvr.gen_dr_en.gen_dr_mode.xcvr_insts[0].gen_xcvr_en.xcvr_inst|directphy_f_dr_0 -entity c7_chip

set_instance_assignment -name IP_RECONFIG_GROUP_MASTER_CLOCK_CHANNEL OFF -to

gen_xcvr.xcvr_i|q0_i|gen_xcvr.gen_dr_en.gen_dr_mode.xcvr_inst|directphy_f_dr_0 -entity c7_chip

set_global_assignment -name IP_RECONFIG_GROUP_PARENT

"TEST:GEN_XCVR.XCVR_I|DDQ0_I|GEN_XCVR.GEN_DR_EN.GEN_DR_MODE.XCVR_INST|DIRECTPHY_F_DR_0/RG_A_E" -entity c7_chip

set_global_assignment -name IP_RECONFIG_GROUP_PARENT

"TEST_WP:GEN_XCVR.XCVR_I|S0_3_I|GEN_XCVR.GEN_DR_EN.GEN_DR_MODE.XCVR_INSTS[0].GEN_XCVR_EN.XCVR_INST|

DIRECTPHY_F_DR_0/RG_A_E" -entity c7_chip

set_global_assignment -name IP_RECONFIG_GROUP_PARENT

"TEST_WP:GEN_XCVR.XCVR_I|S0_3_I|GEN_XCVR.GEN_DR_EN.GEN_DR_MODE.XCVR_INSTS[0].GEN_XCVR_EN.XCVR_INST|

DIRECTPHY_F_DR_0/RG_A_E" -entity c7_chip