Visible to Intel only — GUID: jnc1620090291948

Ixiasoft

Visible to Intel only — GUID: jnc1620090291948

Ixiasoft

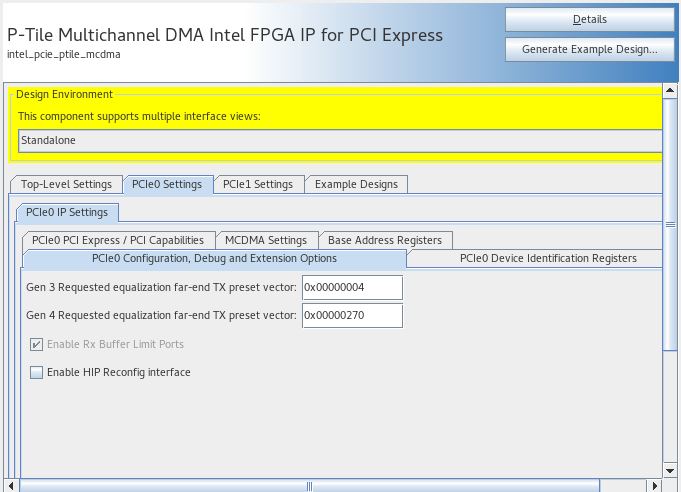

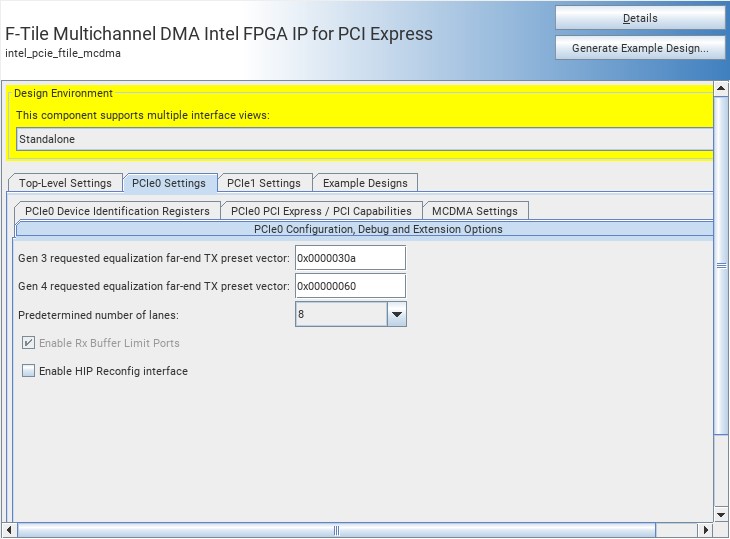

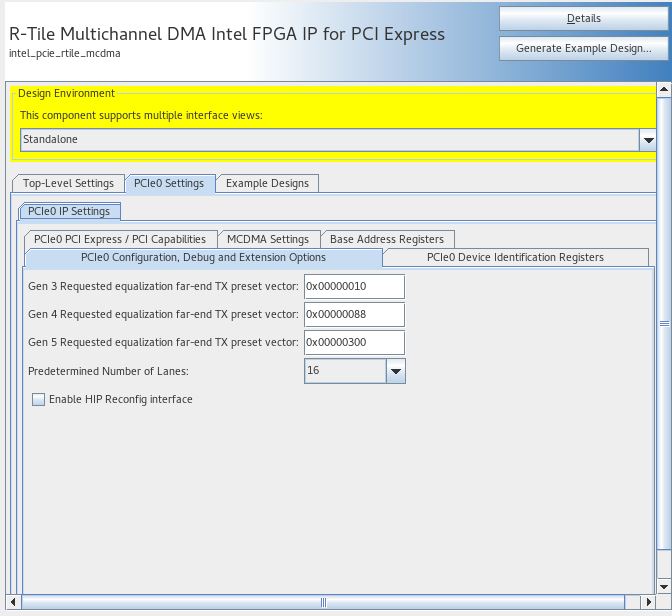

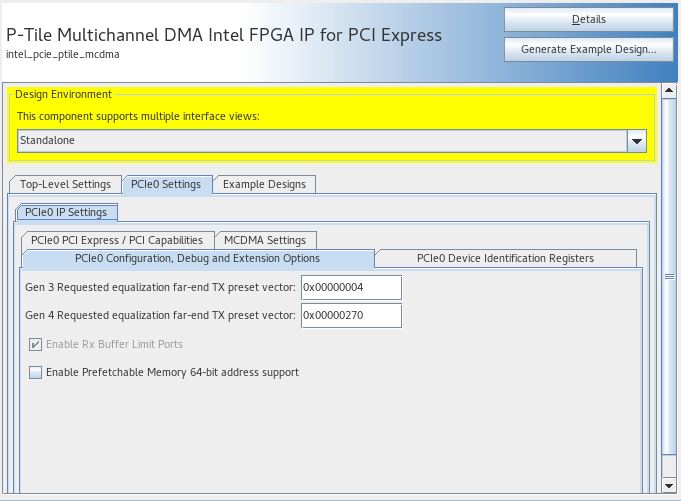

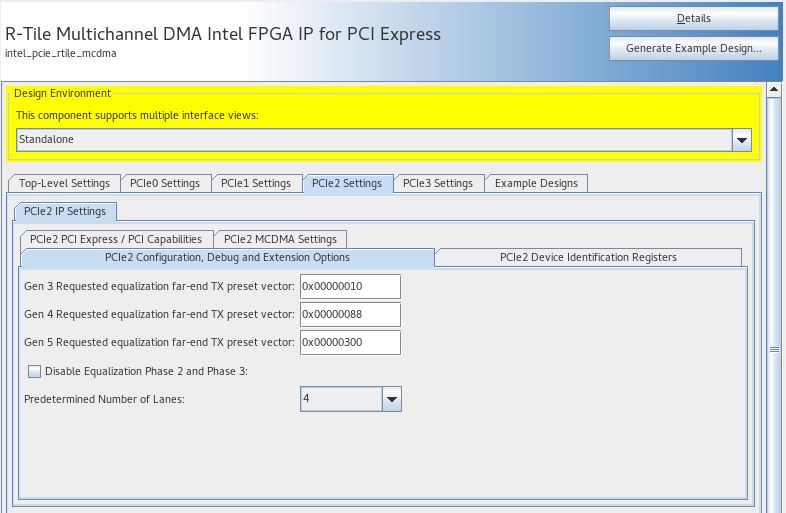

6.2.2. PCIe0 Configuration, Debug and Extension Options

| Parameter | Value | Default Value | Description |

|---|---|---|---|

| Gen 3 Requested equalization far-end TX preset vector |

0 - 65535 |

0x00000004 (for P-Tile) 0x0000030a (for F-Tile) 0x00000200 (for R-Tile Rev. A) 0x00000010 (for R-Tile Rev. B) |

Specifies the Gen 3 requested phase 2/3 far-end TX preset vector. Choosing a value different from the default is not recommended for most designs. |

| Gen 4 Requested equalization far-end TX preset vector |

0 - 65535 |

0x00000270 (for P-Tile) 0x00000360 (for F-Tile) 0x00000008 (for R-Tile Rev. A) 0x00000088 (for R-Tile Rev. B) |

Specifies the Gen 4 requested phase 2/3 far-end TX preset vector. Choosing a value different from the default is not recommended for most designs. |

| Gen5 Requested equalization far-end TX preset vector |

0 - 65535 |

0x00000200 (for R-Tile Rev. A) 0x00000300 (for R-Tile Rev. B) |

Specifies the Gen 5 requested phase 2/3 far-end TX preset vector. Choosing a value different from the default is not recommended for most designs. |

| Predetermined number of lanes (for R-Tile and F-Tile) | 16 8 4 2 1 |

Maximum link width |

Defines the number of lanes which are connected and good. |

| Enable HIP Reconfig interface |

On / Off |

Off | Enables HIP reconfiguration interface

Note: This interface is automatically enabled in Root Port mode. Hence, the parameter is not available for user modification in Root Port mode.

|

| Enable Prefetchable Memory 64-bit address support (Root Port mode only) |

On / Off |

Off | When in RP mode, indicates that the prefetchable memory range supported is 64-bit.

Note: This feature is supported for P-Tile and F-Tile only.

|

| Disable Equalization Phase 2 and Phase3 |

On / Off |

Off | When this parameter is selected, there is no Equalization in Phase 2 and 3 during PCI Express link training.

Note: This feature is only supported for R-Tile and with Root Port mode.

|