Visible to Intel only — GUID: sam1405075821442

Ixiasoft

Design Example Guidelines for Intel® Arria® 10 Devices

These steps are applicable to Intel® Arria® 10 devices using Intel® Quartus® Prime Standard Edition only. Ensure that you use the GPIO Intel® FPGA IP core.

- Open the StratixV_blvds.qar file to import the Stratix® V design example into the Intel® Quartus® Prime Standard Edition software.

- Migrate the design example to use the GPIO Intel® FPGA IP core:

- On the menu, select Project > Upgrade IP Components.

- Double click the "ALIOBUF" entity.

The MegaWizard Plug-In Manager window for the ALTIOBUF IP core appears.

- Turn off Match project/default.

- In Currently selected device family, select Arria 10.

- Click Finish and then click Finish again.

- In the dialog box that appears, click OK.

The Intel® Quartus® Prime Pro Edition software performs the migration process and then displays the GPIO IP parameter editor.

- Configure the GPIO Intel® FPGA IP core to support a bidirectional input and output buffer:

- In Data Direction, select Bidir.

- In Data width, enter 1.

- Turn on Use differential buffer.

- Click Finish and generate the IP core.

- Connect the modules and the input and output ports as shown in the following figure:

Figure 8. Input and Output Ports Connection Example for Intel® Arria® 10 Devices

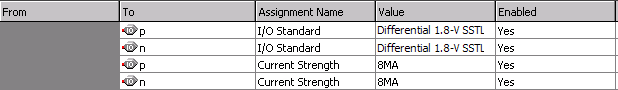

- In the Assignment Editor, assign the relevant I/O standard as shown in the following figure. You can also set the current strength and slew rate options. Otherwise, the Intel® Quartus® Prime Standard Edition software assumes the default settings for Intel® Arria® 10 devices—Differential SSTL-18 Class I or Class II I/O standard.

Figure 9. BLVDS I/O Assignment in the Intel® Quartus® Prime Assignment Editor for Intel® Arria® 10 Devices

Note: For Intel® Arria® 10 devices, you can manually assign both the p and n pin locations for LVDS pins with the Assignment Editor. - Compile and perform functional simulation with the ModelSim* - Intel® FPGA Edition software.