Visible to Intel only — GUID: cno1614291552486

Ixiasoft

5.1. F-Tile Interlaken IP Clock and Reset Interface Signals

5.2. F-Tile Interlaken IP Transmit User Interface Signals

5.3. F-Tile Interlaken IP Receive User Interface Signals

5.4. F-Tile Interlaken IP Management Interface Signals

5.5. F-Tile Interlaken IP Reconfiguration Interface Signals

5.6. F-Tile Interlaken Link and Miscellaneous Signals

Visible to Intel only — GUID: cno1614291552486

Ixiasoft

4.3.2. Multisegments

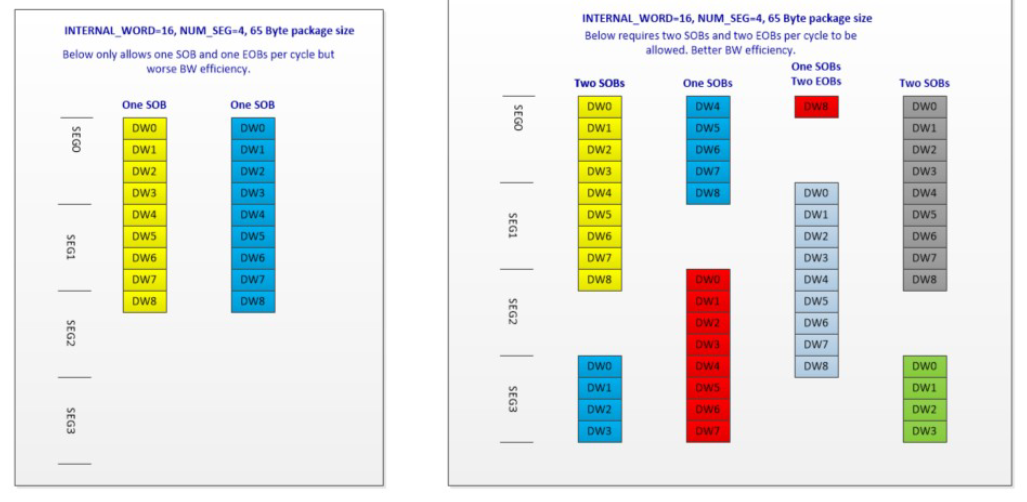

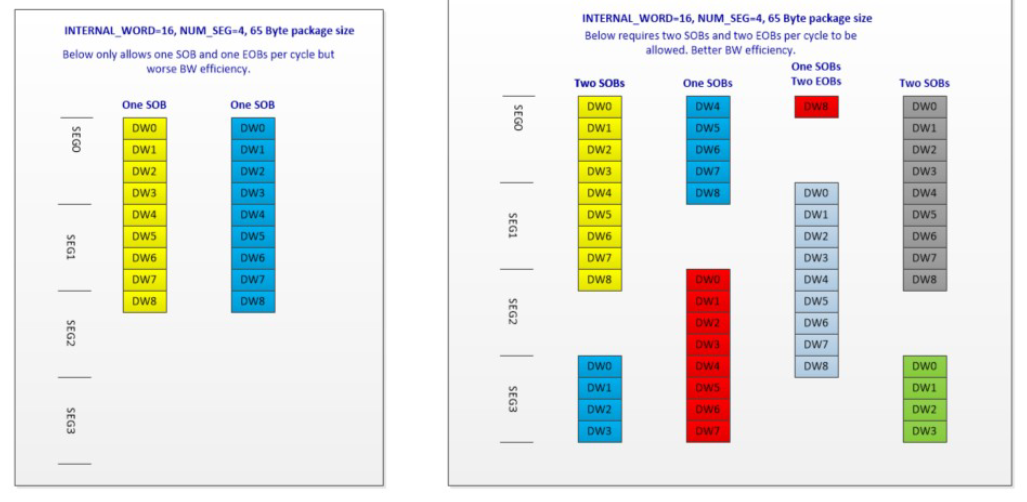

Multisegments in the Interlaken Intel® FPGA IP enable you to make better use of the transmit and receive bandwidth. For package sizes smaller than the user data width, this feature becomes important to provide better bandwidth efficiency.

Figure 22. Interlaken Protocol Layer (MAC)- TX and RX Block Diagram

The user data interface block contains the multisegment blocks, TX and RX regroup. In the TX direction, the TX regroup inserts necessary control words based on the user interface control information before sending downstream for further processing. In the RX direction, the control words of the data received from the striper is stripped off to generate the user data and the extracted control word generates the user interface information.

Figure 23. Four Segment versus Single Segment Bandwidth Efficiency ComparisonThe figure shows the bandwidth efficiency of the four-segment case is significantly better than the single-segment case. Each segment supports both Interleaved and Packet transfer modes when you use multisegments.