Quartus® Prime Pro Edition User Guide: Platform Designer

A newer version of this document is available. Customers should click here to go to the newest version.

Visible to Intel only — GUID: qxr1625161299740

Ixiasoft

Visible to Intel only — GUID: qxr1625161299740

Ixiasoft

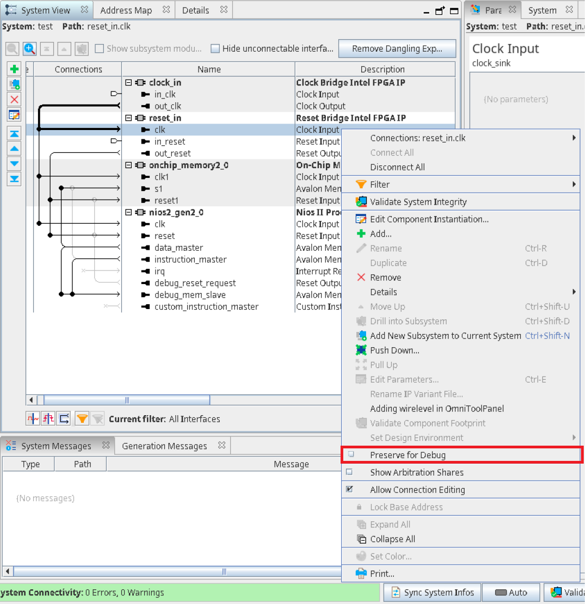

1.15. Preserving System Elements for Debug

You can use any of the following methods to prevent synthesis from performing optimizations on specific modules, interfaces, or port names, allowing the names to persist into the post-fit netlist for Signal Tap and other debug monitoring.

- Enable preserve for debug using any of the following methods:

- On the System View tab, right-click any module, interface or port, and click Preserve for Debug in the context menu.

- On the Filter tab, right-click any module, interface, or port, and click Preserve for Debug in the context menu. A green icon color in the Filter tab indicates that preservation is applied.

- Recompile the design to apply the Preserve for Debug and view the preserved nodes following compilation.