Intel® Stratix® 10 TX Transceiver Signal Integrity Development Kit User Guide

Visible to Intel only — GUID: sma1529450878503

Ixiasoft

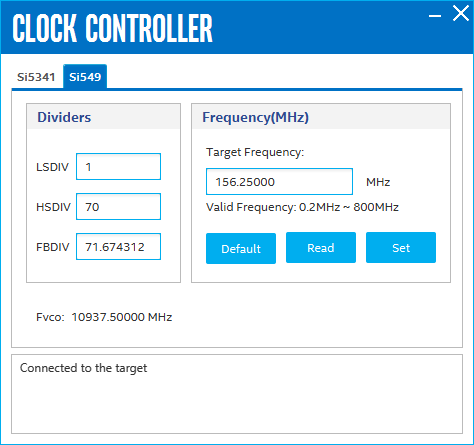

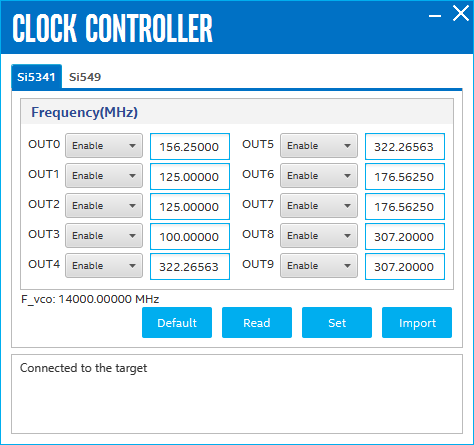

5.3.11. Clock Controller

The Clock Controller application sets the Si549 programmable oscillators to any frequency between 0.2 MHz and 800 MHz and sets the Si5341 PLL to any frequencies between 10 MHz and 750 MHz. The oscillator drives a 2-to-6 buffer that drives a copy of the clock to all transceiver blocks of the FPGA.

To start the application, click Clock Controller icon in the BTS. You can also run the Clock Controller as a stand-alone application.

The ClockController.exe resides in the <package dir>\examples\board_test_system directory.

The Clock Control communicates with the MAX V device on the board through the JTAG bus. The Si549 programmable oscillator and PLL are connected to the MAX V device through a 2-wire bus.

The following sections describe the Clock Control controls.

Divider

Fvco

Target Frequency

The Target Frequency control allows you to specify the frequency of the clock. Legal values are between 0.2 MHz and 800 MHz and select frequencies to 1400 MHz. For example, 421.31259873 is possible within 100 parts per million (ppm). The Target Frequency control works in conjunction with the Set Control.

Set

The Set control sets programmable oscillator or PLL frequency to the value in the Target frequency control. Frequency changes might take several milliseconds to take effect. You might see glitches on the clock during this time.

Default

Sets the frequency for the oscillator associated with the active tab back to its default value. This can also be accomplished by power cycling the board.