Visible to Intel only — GUID: ymy1654131014566

Ixiasoft

1. About the R-Tile Avalon® Streaming Intel® FPGA IP for PCI Express

2. IP Architecture and Functional Description

3. Advanced Features

4. Interfaces

5. Parameters

6. Troubleshooting/Debugging

7. R-Tile Avalon® Streaming Intel® FPGA IP for PCI Express* User Guide Archives

8. Document Revision History for the R-Tile Avalon® Streaming Intel FPGA IP for PCI Express User Guide

A. Configuration Space Registers

B. Root Port Enumeration

C. Implementation of Address Translation Services (ATS) in Endpoint Mode

D. Packets Forwarded to the User Application in TLP Bypass Mode

E. Margin Masks for the R-Tile Avalon Streaming Intel FPGA IP for PCI Express

3.2.2.5.1. VirtIO Common Configuration Capability Register (Address: 0x012)

3.2.2.5.2. VirtIO Common Configuration BAR Indicator Register (Address: 0x013)

3.2.2.5.3. VirtIO Common Configuration BAR Offset Register (Address: 0x014)

3.2.2.5.4. VirtIO Common Configuration Structure Length Register (Address 0x015)

3.2.2.5.5. VirtIO Notifications Capability Register (Address: 0x016)

3.2.2.5.6. VirtIO Notifications BAR Indicator Register (Address: 0x017)

3.2.2.5.7. VirtIO Notifications BAR Offset Register (Address: 0x018)

3.2.2.5.8. VirtIO Notifications Structure Length Register (Address: 0x019)

3.2.2.5.9. VirtIO Notifications Notify Off Multiplier Register (Address: 0x01A)

3.2.2.5.10. VirtIO ISR Status Capability Register (Address: 0x02F)

3.2.2.5.11. VirtIO ISR Status BAR Indicator Register (Address: 0x030)

3.2.2.5.12. VirtIO ISR Status BAR Offset Register (Address: 0x031)

3.2.2.5.13. VirtIO ISR Status Structure Length Register (Address: 0x032)

3.2.2.5.14. VirtIO Device Specific Capability Register (Address: 0x033)

3.2.2.5.15. VirtIO Device Specific BAR Indicator Register (Address: 0x034)

3.2.2.5.16. VirtIO Device Specific BAR Offset Register (Address 0x035)

3.2.2.5.17. VirtIO Device Specific Structure Length Register (Address: 0x036)

3.2.2.5.18. VirtIO PCI Configuration Access Capability Register (Address: 0x037)

3.2.2.5.19. VirtIO PCI Configuration Access BAR Indicator Register (Address: 0x038)

3.2.2.5.20. VirtIO PCI Configuration Access BAR Offset Register (Address: 0x039)

3.2.2.5.21. VirtIO PCI Configuration Access Structure Length Register (Address: 0x03A)

3.2.2.5.22. VirtIO PCI Configuration Access Data Register (Address: 0x03B)

4.3.1. Avalon® Streaming Interface

4.3.2. Precision Time Measurement (PTM) Interface (Endpoint Only)

4.3.3. Interrupt Interface

4.3.4. Hard IP Reconfiguration Interface

4.3.5. Error Interface

4.3.6. Completion Timeout Interface

4.3.7. Configuration Intercept Interface

4.3.8. Power Management Interface

4.3.9. Hard IP Status Interface

4.3.10. Page Request Services (PRS) Interface (Endpoint Only)

4.3.11. Function-Level Reset (FLR) Interface (Endpoint Only)

4.3.12. SR-IOV VF Error Flag Interface (Endpoint Only)

4.3.13. General Purpose VSEC Interface

5.2.3.1. Device Capabilities

5.2.3.2. VirtIO Parameters

5.2.3.3. Link Capabilities

5.2.3.4. Legacy Interrupt Pin Register

5.2.3.5. MSI Capabilities

5.2.3.6. MSI-X Capabilities

5.2.3.7. Slot Capabilities

5.2.3.8. Latency Tolerance Reporting (LTR)

5.2.3.9. Process Address Space ID (PASID)

5.2.3.10. Device Serial Number Capability

5.2.3.11. Page Request Service (PRS)

5.2.3.12. Access Control Service (ACS)

5.2.3.13. Power Management

5.2.3.14. Vendor Specific Extended Capability (VSEC) Registers

5.2.3.15. TLP Processing Hints (TPH)

5.2.3.16. Address Translation Services (ATS) Capabilities

5.2.3.17. Precision Time Measurement (PTM)

Visible to Intel only — GUID: ymy1654131014566

Ixiasoft

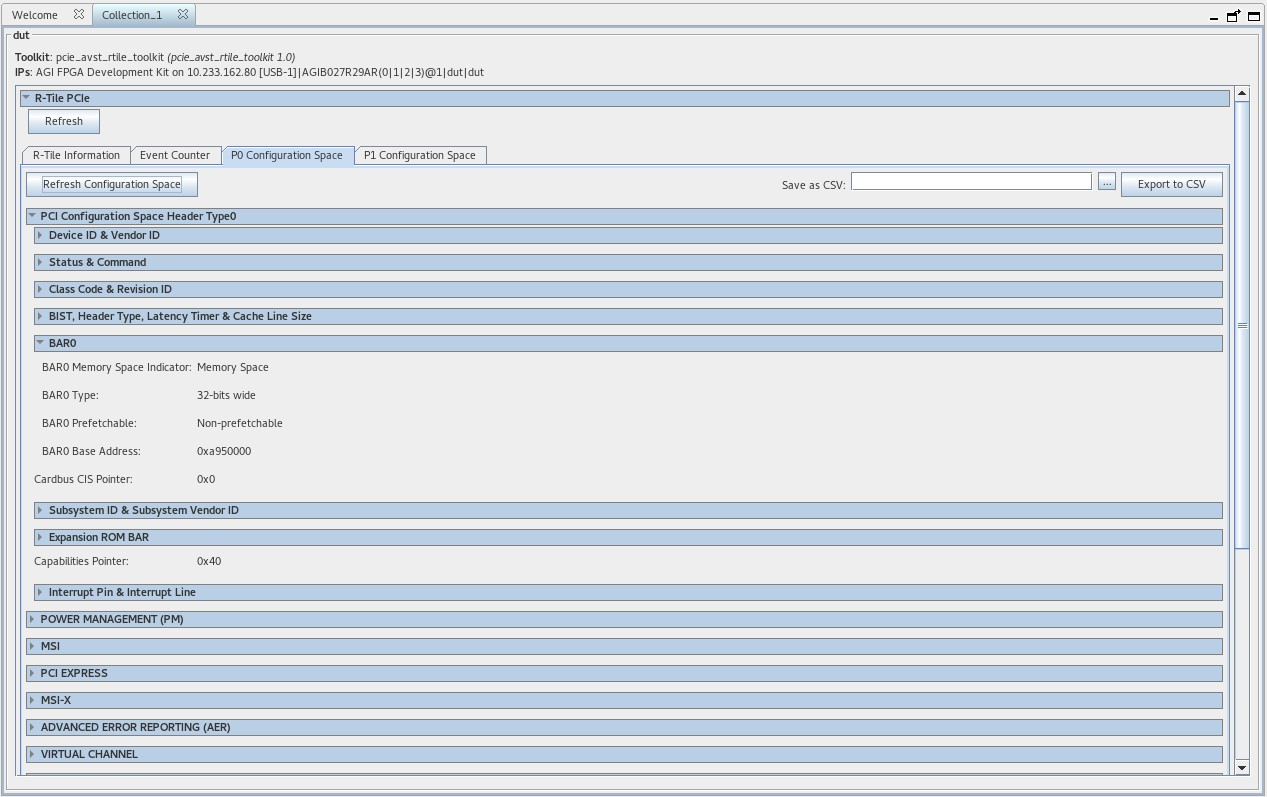

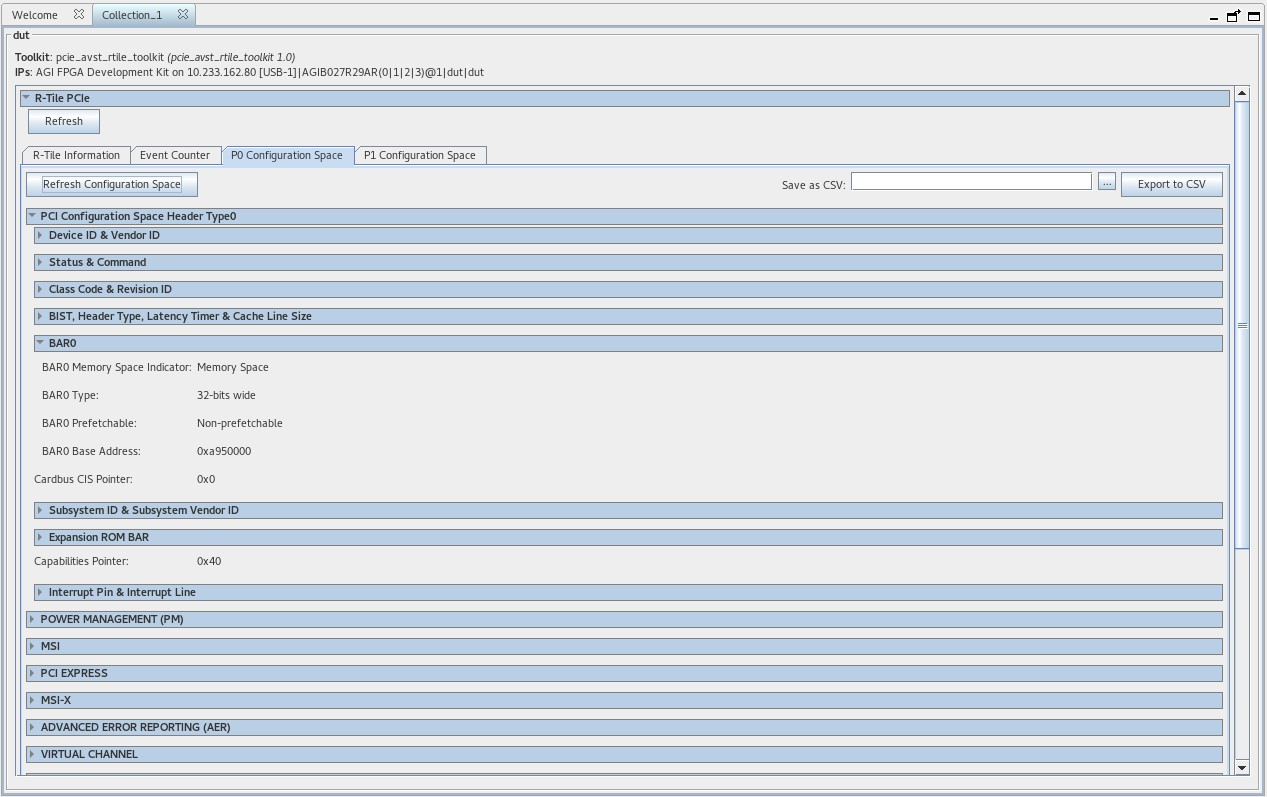

6.6.4.4. Configuration Space

This tab allows you to read the configuration space registers directly, without the need to issue a Configuration Read from the link partner. Depending on the Hard IP Mode selected during the IP configuration (for example Gen5 2x8), you will see a separate tab with the configuration space for each port. Also, please note that:

- All the information is read-only.

- The per-lane information under the tab Configuration Space corresponds to the logical lanes.

- Use the Refresh Configuration Space button to read the Configuration Space registers.

Figure 67. Configuration Space Tab