Using the Transceiver Reconfiguration Controller for Dynamic Reconfiguration in Arria V and Cyclone V Devices

1.4.3. Creating the Reconfiguration Controller

The Reconfiguration Controller controls the dynamic reconfiguration of Arria V and Cyclone V PHY IPs.

The following steps describe how to set up the Reconfiguration Controller to dynamically control the PMA settings, change the PLL selection by streaming a MIF, and trigger DCD calibration manually.

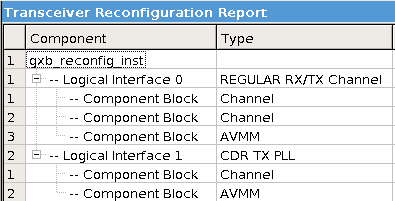

The Native PHY IP created in the previous section requires two reconfiguration interfaces, one for the REGULAR RX/TX Channel and one for the CDR TX PLL, as shown in the following figure. You can verify the logical interface information in the Transceiver Reconfiguration Report.

The Transceiver Reconfiguration Report is located under Fitter Report > GXB Report.

Refer to the parameters setting in the figure below to set up the Interface Bundles, Transceiver Calibration functions, Analog Features, and Reconfiguration Features functions.

The Interface Bundles section specifies two interface bundles. The first interface is connected to the RX/TX channels as shown in Figure 5. The second interface is connected to the CMU PLL.

The following table shows the Interface Bundles connection in the top-level design file a5_top.v.

| Reconfiguration Ports |

Native PHY/ CMU PLL Ports |

Connected to |

|---|---|---|

| [69:0] ch0_0_to_xcvr [45:0] ch0_0_from_xcvr |

[69:0] reconfig_to_xcvr [45:0] reconfig_from_xcvr |

Connected to RX/TX channel |

| [69:0] ch1_1_to_xcvr [45:0] ch1_1_from_xcvr |

[69:0] reconfig_to_cmu [45:0] reconfig_from_cmu |

Connected to CMU PLL |

In the Transceiver Calibration Functions section, turn on the Enable duty cycle calibration option.

In the Analog Features section, turn on the Enable Analog controls option to enable VOD setting reconfiguration.

In the Reconfiguration Features section, turn on the Enable channel/PLL reconfiguration option to allow the streamer-based reconfiguration process. This reconfiguration mode reconfigures the TX/RX data path, CDR settings, and TX PLL selection.

After all parameters have been specified, you can generate the Reconfiguration Controller.