Visible to Intel only — GUID: nln1726239350498

Ixiasoft

Visible to Intel only — GUID: nln1726239350498

Ixiasoft

2.4.2.1. Deprecation of the blackbox Argument

Going forward, you can use set_max_delay constraints to perform delay budgeting on I/Os at the boundary of a design partition, rather than using the blackbox argument. The following example shows how to convert a set_output_delay -blackbox constraint to a set_max_delay constraint.

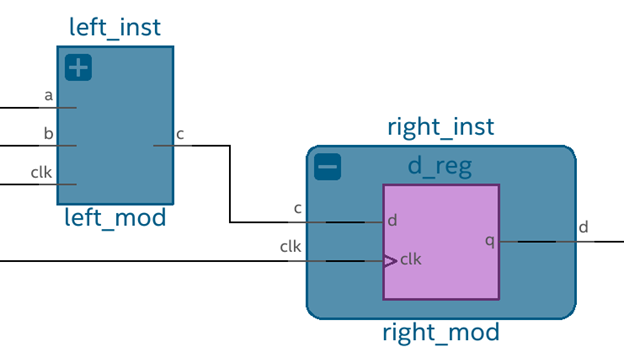

Sample Design Hierarchy with Design Partitions shows a sample design hierarchy, where left_inst and right_inst are partitions, and the c pins of each partition are the partition boundaries.

The module for right_inst is not yet available to the developer, and is represented by a single register, d_reg. The clock has a period of 4 ns.

To ensure that the path between left_inst and right_inst can pass timing after the right_inst module is available, the left_inst partition must not use the entire 4 ns available for the data transfer.

In previous versions of the Quartus® Prime Pro Edition software, you could use a set of constraints like the following:

set budget 2.5 set ref_pin [get_pins right_inst|d_reg|clk] set_output_delay -clock clk -blackbox -reference_pin $ref_pin $budget [get_pins right_inst|c]

The example constraints set a delay budget of 2.5ns to right_inst, leaving a delay budget of 1.5ns for the left_inst partition. However, these example constraints require that you also specify the correct reference pin to accurately measure the impact of clock skew.

Beginning in Quartus® Prime Pro Edition version 24.3, as an alternative to the delay budgeting approach, use the following technique. This technique is simpler, and automatically includes clock skew impact without requiring you to specify a reference pin.

set period 4

set budget 2.5

set_max_delay [expr {$period - $budget}] -through [get_pins right_inst|c]