Quartus® Prime Pro Edition User Guide: Timing Analyzer

A newer version of this document is available. Customers should click here to go to the newest version.

Visible to Intel only — GUID: zne1707241736818

Ixiasoft

Visible to Intel only — GUID: zne1707241736818

Ixiasoft

2.3.5.2.4. Exporting a Design Partition with Entity-bound Constraints

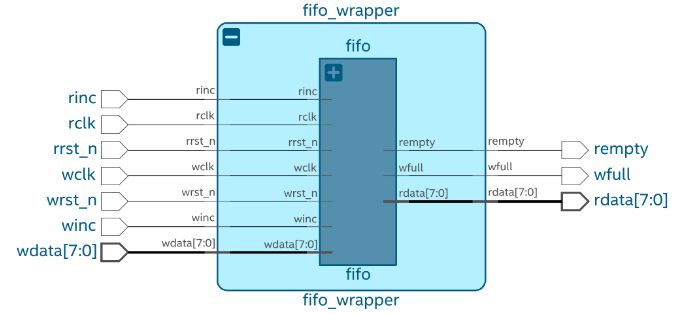

The following example illustrates exporting a partition that includes entity bound constraints for use in another project. This example uses the fifo entity.

Perform these steps to export a design partition with entity-bound constraints:

- After applying the constraints to the fifo entity, click Fitter on the Compilation Dashboard to run the Fitter. The Messages window report when the Fitter is complete.

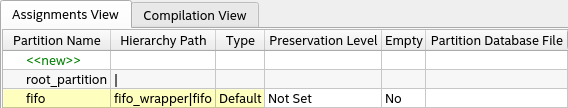

- Click Assignments > Design Partitions Window and define Default Type design partition for the fifo entity in the Assignments View tab of the Design Partition dialog box.

Figure 78. Assignments View of the Design Partition Window

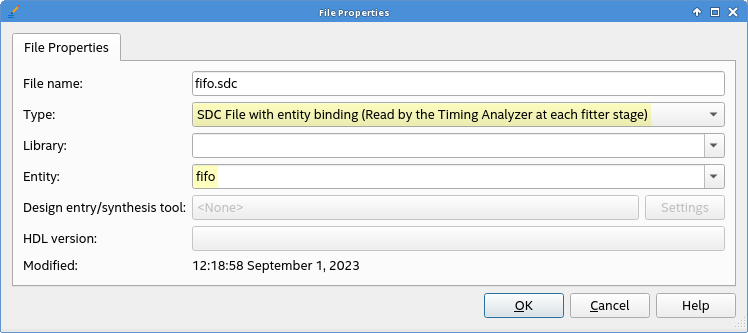

- Specify the entity-bound SDC File name and Type to establish the binding between the fifo entity and the .sdc file.

Figure 79. File Properties Dialog

- Click Compile Design on the Compilation Dashboard to run a full compilation and apply the changes to your project. The Timing Analyzer opens by default following a successful full compilation.

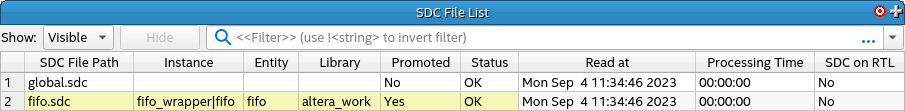

- Confirm the correct association of the .sdc file with the fifo entity by reviewing the SDC File List report in the Timing Analyzer.

Figure 80. SDC File List Report in the Timing Analyzer

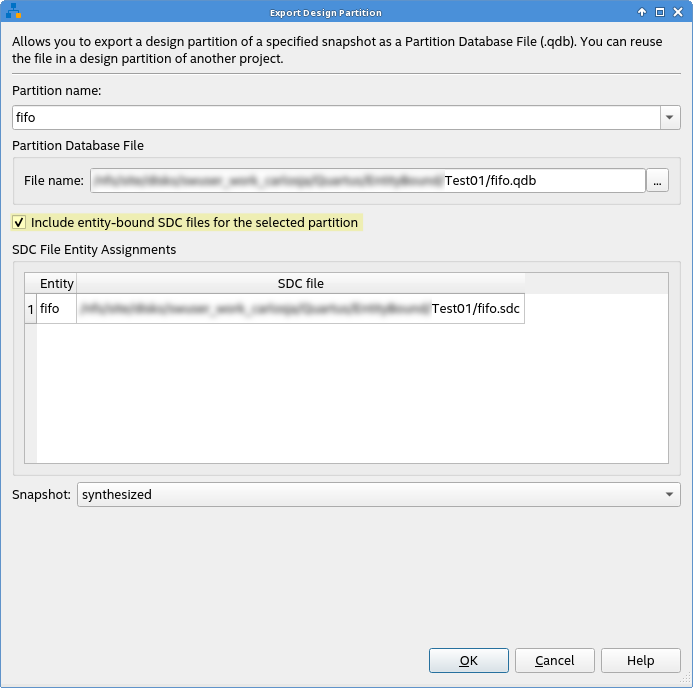

- Click Project > Export Design Partition and specify the following options:

- In the Partition name list, select the partition to export.

- In Partition Database File, specify the partition database file.

- Turn on the Include entity-bound SDC files for the selected partition option for entity-bound SDC files linked to the chosen partitions.

- For Snapshot, specify Synthesized or Final.

Figure 81. Export Design Partition Dialog