Visible to Intel only — GUID: buo1730469296228

Ixiasoft

Visible to Intel only — GUID: buo1730469296228

Ixiasoft

3.1.3.3.2. Constraining Synchronizers in CDCs

You can identify any unconstrained synchronizers in the Report Asynchronous CDC report under Unconstrained Transfer. In addition, the Design Assistant reports unconstrained synchronizers under the CDC-50002 - 1-Bit Asynchronous Transfer with Insufficient Constraints rule.

In the Quartus Prime Timing Analyzer, you specify timing constraints using Synopsys Design Constraints (SDC) files. With respect to clock domain crossings, SDC timing constraints allow you to identify paths that cross clock domains. For signals that you can safely synchronize using a CDC synchronizer,use SDC constraints to define the path to the first register in the synchronizer chain as false path. This false path constraint informs the Timing Analyzer not to consider these paths for timing analysis because the synchronizer handles them.

SDC also allows you to define clock groups that you can use to specify asynchronous clock relationships. Specifying such a relationship is important for CDC analysis because it indicates to the Timing Analyzer whether clocks do not have a phase or frequency relationship and may require special consideration for data transfer.

The following example shows basic SDC constraints for a synchronizer. The two clock domain definitions are first. Next, the set_clock_groups command clarifies that both clocks are asynchronous and are unrelated. Alternatively, set_false_path excludes the path that crosses between clock domains from timing analysis.

# Define the clocks (assuming clock names are clk1 and clk2 for the two domains) create_clock -name clk1 -period 10 [get_ports clk1] create_clock -name clk2 -period 20 [get_ports clk2] # Group the clocks to specify that they are asynchronous to each other set_clock_groups -asynchronous -group [get_clocks clk1] -group [get_clocks clk2] # Specify false path for the CDC path between the two clock domains set_false_path -from [get_registers reg_clk1] -to [get_registers sync_ff[0]]

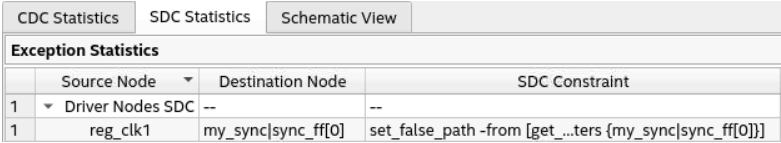

When you appropriately define and constrain a CDC, the Report Asynchronous CDC report indicates that the CDC is time-compliant, and provides additional details about SDC constraints on the SDC Statistics tab. Use the SDC Statistics tab to corroborate the correct application of the false path between the register in the transmitter clock domain, and the first stage of the synchronizer in the receiver clock domain.

The SDC Statistics then presents basic information such as the source register and the registers that form the synchronizer.

The Schematic View provides a representation of the synchronizer. The light green line between reg_clk1 and sync_ff[0] registers indicates that there is a false path exception on the path. Right-click on the background of the Schematic View tab and choose Color Legend to display the color legend.

The Setup Transfers and Hold Transfers reports indicate that timing analysis ignores the path crossing from clk1 to clk2 because it is a false path.

Correct RTL coding and accurate constraint definition for synchronizers in clock domain crossings are essential for robust digital designs. Defining the RTL structure of synchronizers improves the reliability of data transfers across asynchronous clock domains and ensures signal integrity, thereby minimizing the risk of metastability. Complemented with exact timing constraints, the Quartus Prime software can correctly interpret and implement the synchronizers during the Fitter. Such a method simplifies timing analysis, guarantees that all CDC paths satisfy their timing requirements, and enhances the design's overall performance.