Quartus® Prime Pro Edition User Guide: Timing Analyzer

A newer version of this document is available. Customers should click here to go to the newest version.

Visible to Intel only — GUID: coj1707242724835

Ixiasoft

Visible to Intel only — GUID: coj1707242724835

Ixiasoft

2.3.5.2.5. Importing a Design Partition with Entity-bound Constraints

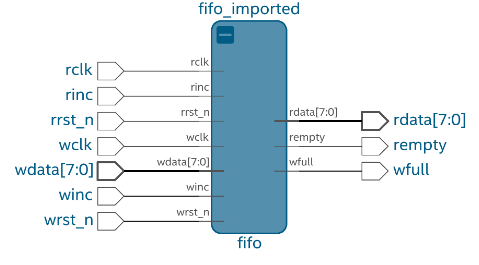

Importing a partition with entity-bound SDC files requires that you define a black box wrapper for the entity in your design. This wrapper declares a partition in which the data from the imported partition is utilized. Consider the following example with an entity named fifo_imported:

To import a design partition with entity-bound constraints, perform these steps:

- To run design synthesis, click Analysis & Synthesis on the Compilation Dashboard.

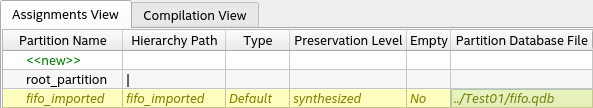

- To create a new partition within the wrapper entity, click Assignments > Design Partitions Window and specify the following options on the Assignments View tab:

- Specify the Partition Name and the Hierarchy Path of the entity instance.

- Specify Default for the partition Type.

- Specify synthesized in the Preservation Level column.

- Specify the .qdb file from the previous project as the Partition Database File

Figure 83. Assignments View of the Design Partition Dialog

- To run a full compilation, click Compile Design on the Compilation Dashboard. The Timing Analyzer appears automatically following successful compilation.

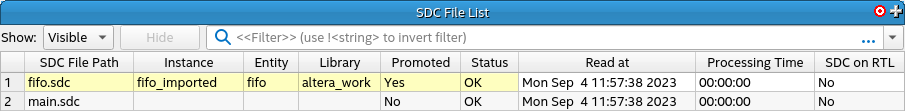

- Verify the correct application of the entity-bound SDC file assignment in the SDC File List report.

Figure 84. SDC File List Report in the Timing Analyzer