Quartus® Prime Pro Edition User Guide: Timing Analyzer

A newer version of this document is available. Customers should click here to go to the newest version.

Visible to Intel only — GUID: ntz1535573669856

Ixiasoft

Visible to Intel only — GUID: ntz1535573669856

Ixiasoft

2.3.5.2.2. Automatic Scope Entity-bound Constraint Example

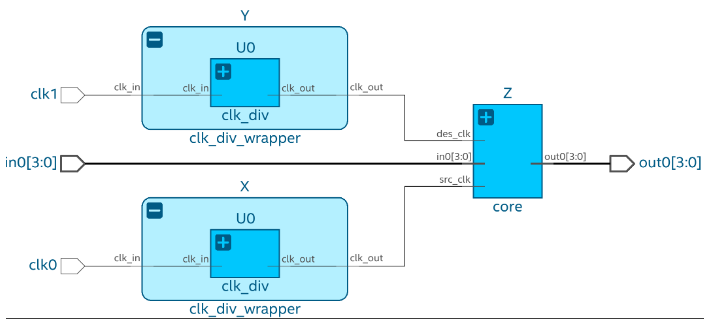

In the following design, two instances of the clk_div entity are constrained using the entity-bound SDC file approach. After running the Fitter's Plan stage and the timing netlist becomes available, follow the steps below to associate an SDC file with a particular entity in your design:

- Create a non-entity-bound SDC file that defines constraints targeted by a global scope and add it to the project. For this design, two clocks (clk0 and clk1 are defined.

# global.sdc create_clock -period 100MHz -name clk_100 [get_ports clk0] create_clock -period 75MHz -name clk_75 [get_ports clk1]

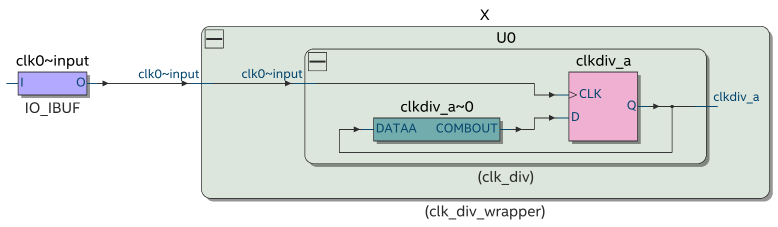

- Create a second SDC file to constrain your target entity and add it to the project. This file follows the entity-bound approach and associates with the clk_div entity. Consequently, you define constraints as if this entity were at the top-level hierarchy, with path names relative to the entity. For example, the get_pins clkdiv_a|q command does not require the X|U0 hierarchy. In this example, the get_current_instance Tcl command generates a unique name for each clock.

In this specific case, the .sdc file creates a new clock on the output of the module, and the get_current_instance Tcl command generates a unique name for each clock.

# clk_div.sdc set unique_clock_name "[get_current_instance]_clkout" create_generated_clock -divide_by 2 -source [get_pins clkdiv_a|clk] -name $unique_clock_name [get_pins clkdiv_a|q]

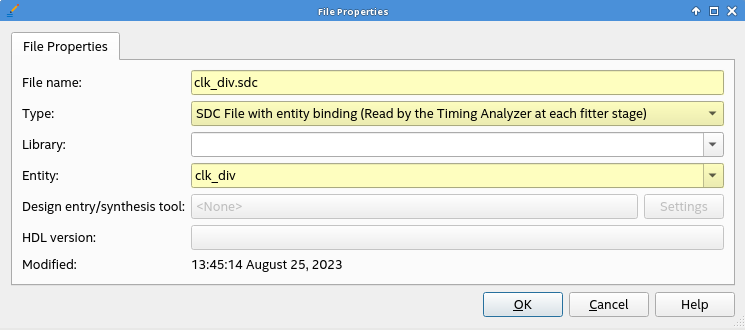

- Open the File Properties dialog for the .sdc file associated with the clk_div entity from the files list in the left-hand Project Tasks pane.

- Select the SDC File with entity binding (Read by the Timing Analyzer at each fitter stage) option in the Type list.

- In the Entity list, select clk_div .

This step applies automatic scoping to the entity-bound file, where all paths in filter commands are prepended with the top-level path of the current hierarchy. For instance, the command get_registers clkdiv_a is dynamically transformed into its fully hierarchical counterpart, such as get_registers X|U0|clkdiv_a.

Note: You must first complete Analysis & Synthesis to populate the list of entities.

Figure 72. File Properties Dialog

Alternatively, you can use the following .qsf assignment to set the entity binding:

set_global_assignment -name SDC_ENTITY_FILE clk_div.sdc -entity clk_div

- Recompile the project to apply the changes. This results in the corresponding .sdc file being effectively bound to the entity in the automatic scope mode.

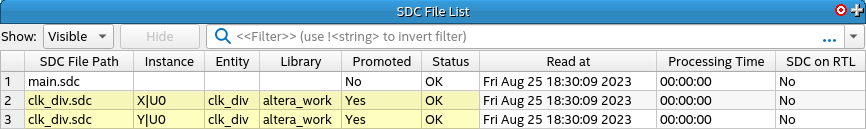

- Verify the implementation of the entity-bound property by reviewing the SDC File List report in the Timing Analyzer. This report provides a comprehensive list of the applied SDC files for the design. For entity-bound SDC files, the report includes the associated instance, entity name, library, and the status of automatic scoping:

Figure 73. SDC File List Report in the Timing Analyzer

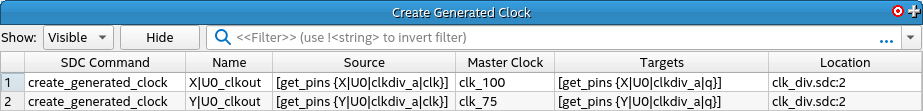

- Determine the correct application of each constraint according to the intended purpose. For example, examine the generated clocks and cross-reference with the clock hierarchy to determine if the constraints are successfully applied, as shown in the following images:

Figure 74. Create Generated Clock Window in the Timing Analyzer

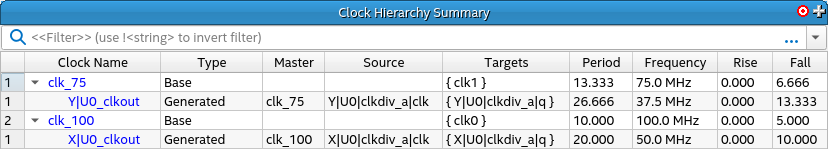

Figure 75. Clock Hierarchy Summary Window in the Timing Analyzer

Figure 75. Clock Hierarchy Summary Window in the Timing Analyzer