Quartus® Prime Pro Edition User Guide: Timing Analyzer

A newer version of this document is available. Customers should click here to go to the newest version.

Visible to Intel only — GUID: row1706912461580

Ixiasoft

Visible to Intel only — GUID: row1706912461580

Ixiasoft

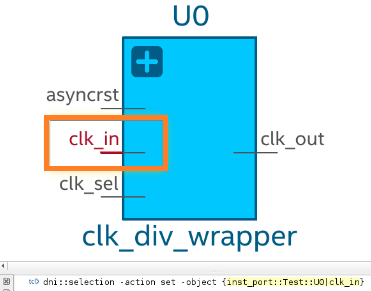

2.3.5.1.1. Targeting Constraints to Module Inputs and Outputs

SDC-on-RTL allows you to define constraints at module boundaries, even if some internal connections within the modules or IP remain partially unknown. It is best to apply SDC-on-RTL constraints at the module boundaries, specifically at the input and output boundaries of each module.

When targeting your timing constraints to the inputs and outputs of a module, you can target the following different element types, depending on your circumstances:

# inside

get_pins {clk_in} clk_dic.rtlsdc