Visible to Intel only — GUID: pwk1702492908254

Ixiasoft

2.1. Device Footprint

2.2. Power Management

2.3. Configuration

2.4. Design Security Differences

2.5. Logic Elements and Embedded Memory

2.6. PLL and Clock Network

2.7. Digital Signal Processing (DSP)

2.8. I/O Interfaces

2.9. LVDS SERDES Interface

2.10. Sensor Monitoring System

2.11. MIPI D-PHY Interface

2.12. External Memory Interface (EMIF)

2.13. Hard Processor System (HPS)

2.14. Transceiver and Serial Protocols

2.15. PCIe Interface

2.16. Ethernet Interface

2.3.1. General Configuration Pin and Sequences

2.3.2. Device Configuration and the Secure Device Manager (SDM)

2.3.3. Active Serial (AS) Configuration

2.3.4. Avalon® -ST Configuration

2.3.5. JTAG Configuration

2.3.6. Configuration via Protocol (CvP)

2.3.7. QSPI Flash Access and Remote System Upgrade Feature

2.3.8. SEU Features

2.3.9. Configuration File Format Differences

Visible to Intel only — GUID: pwk1702492908254

Ixiasoft

4.3.5. Compiling the Design

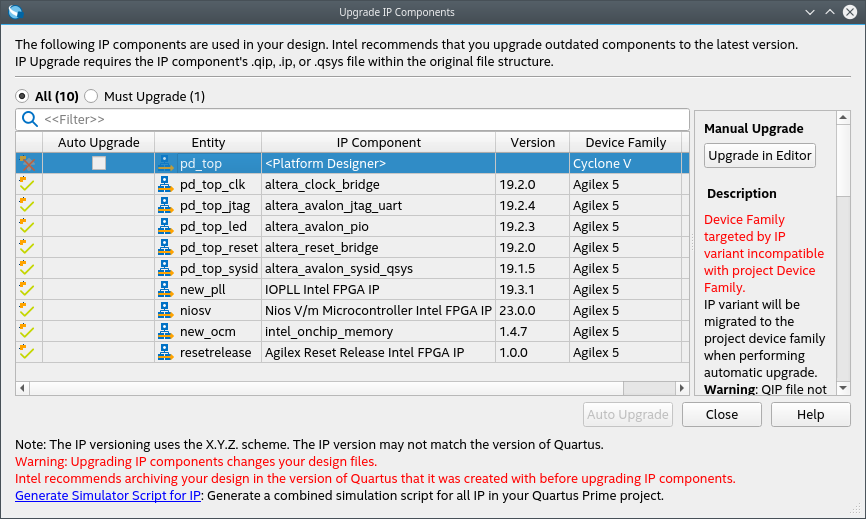

After upgrading the IP cores in the Platform Designer, the Upgrade IP Components is updated to match the current files and IP components available in the current design.

Figure 32. Upgrade IP Components Dialog

As you can observe, the IP cores have been automatically upgraded to target Agilex™ 5. The Cyclone® V-targeted pd_top entity cannot be removed as it is a Platform Designer file. You continue to see it because the QIP file is still included in the project.

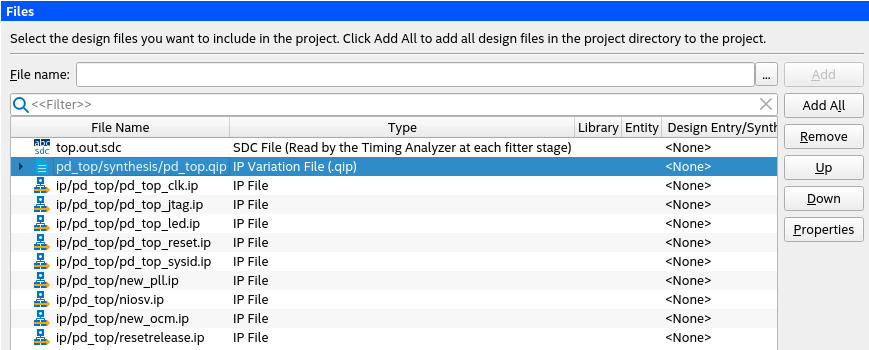

To remove the pd_top file, perform the following steps:

- Click Project > Add/Remove Files in Project.

- Remove the pd_top.qip file in the Files dialog.

Figure 33. Files Dialog

- Click Apply.

- Click OK. The IP Upgrade Required sign disappears.

- Compile the design by clicking Processing > Start Compilation. Compilation might take about 10 minutes to complete. Once the compilation ends, you have successfully completed the design migration from Cyclone® V to the Agilex™ 5 device.