Visible to Intel only — GUID: qki1686138398648

Ixiasoft

1. About the Drive-on-Chip Design Example for Intel Agilex® 7 Devices

2. Features of the Drive-on-Chip Design Example for Intel Agilex 7 Devices

3. Getting Started with the Drive-on-Chip Design Example for Intel Agilex 7 Devices

4. Rebuilding the Drive-on-Chip Design Example for Intel Agilex 7 Devices

5. About the Scaling of Feedback Signals

6. Motor Control Software

7. Functional Description of the Drive-on-Chip Design Example for Intel Agilex 7 Devices

8. Signals

9. Registers

10. Design Security Recommendations

11. Document Revision History for AN 994: Drive-on-Chip Design Example for Intel Agilex 7 Devices

3.1. Software Requirements for the Drive-on-Chip Design Example for Intel Agilex 7 Devices

3.2. Hardware Requirements for the Drive-on-Chip Design Example for Intel Agilex 7 Devices

3.3. Downloading and Installing the Design

3.4. Setting Up your Development Board for the Drive-on-Chip Design Example for Intel Agilex 7 Devices

3.5. Configuring the FPGA Hardware for the Drive-on-Chip Design Example for Intel Agilex 7 Devices

3.6. Programming the Nios V/g Software to the Device for the Drive-on-Chip Design Example for Intel Agilex 7 Devices

3.7. Debugging and Monitoring the Drive-on-Chip Design Example for Intel Agilex 7 Devices with Python GUI

3.7.1. GUI Control Parameters Pane for the Drive-on-Chip Design Example for Intel Agilex 7 Devices

3.7.2. GUI Main Panes for the Drive-on-Chip Design Example for Intel Agilex 7 Devices

3.7.3. Tuning the PI Controller Gains

3.7.4. Controlling the Speed and Position Demonstrations

3.7.5. Monitoring Performance

7.3.6.1. DSP Builder for Intel FPGAs Model for the Drive-on-Chip Designs

7.3.6.2. Avalon Memory-Mapped Interface

7.3.6.3. About DSP Builder for Intel FPGAs

7.3.6.4. DSP Builder for Intel FPGAs Folding

7.3.6.5. DSP Builder for Intel FPGAs Design Guidelines

7.3.6.6. Generating VHDL for the DSP Builder Models for the Drive-on-Chip Designs

Visible to Intel only — GUID: qki1686138398648

Ixiasoft

3.6. Programming the Nios V/g Software to the Device for the Drive-on-Chip Design Example for Intel Agilex 7 Devices

- Program top.sof.

The software is automatically copied to the CPU memories for running using .hex files located in <project>/software/dniosv_subsystem/build/bin/mem_init to initialize the memories in the system.

- Run the JTAG UART terminal to see the design software application output.

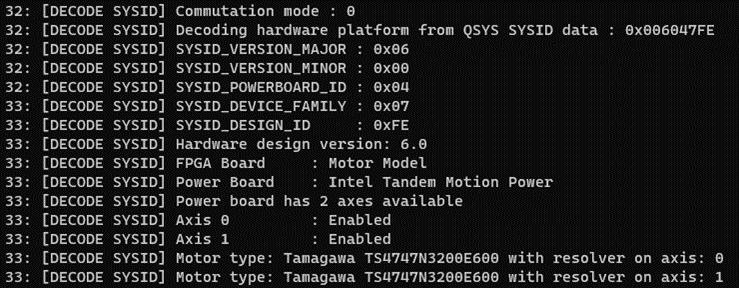

Figure 5. Software application Output

- If you modify the software, program the Nios V soft processor using the command line:

>>niosv-download <project>/software/dniosv_subsystem/build/bin/app.elf -g