3.3.1. RS-FEC Modes

| Supported RS-FEC Modes | RS-FEC Receives Data From | Example Applications | Details |

|---|---|---|---|

| Fractured | EHIP_LANE | 25GbE - NRZ w/FEC (528, 514) |

You can configure all six FEC blocks per E-tile in this mode. NRZ mode: Four lanes within a FEC block operate independently for single lane protocols. However, RS-FEC needs to be shared among the NRZ channels within one IP instantiation. |

| FPGA core | CPRI 24G - NRZ w/ FEC (528, 514) 32GFC w/ FEC (528, 514) |

||

| Aggregate | EHIP_CORE | 100GbE (4 x 25G) – NRZ w/ FEC (528, 514) 100GbE (2 x 50G) – PAM4 w/ FEC (544, 514) |

You can configure a maximum of four out of six FEC blocks per E-tile in this mode. Refer to E-Tile Floor Plan Configurations for more details. Four lanes of a FEC block are used together for multi-lane protocols, like 100GbE. |

| PMA Direct | 128 GFC | ||

| Bypass | — | 10GbE – NRZ 25GbE - NRZ w/o FEC 100GbE (4 x 25G) – NRZ w/o FEC |

Protocols or applications that do not need RS-FEC |

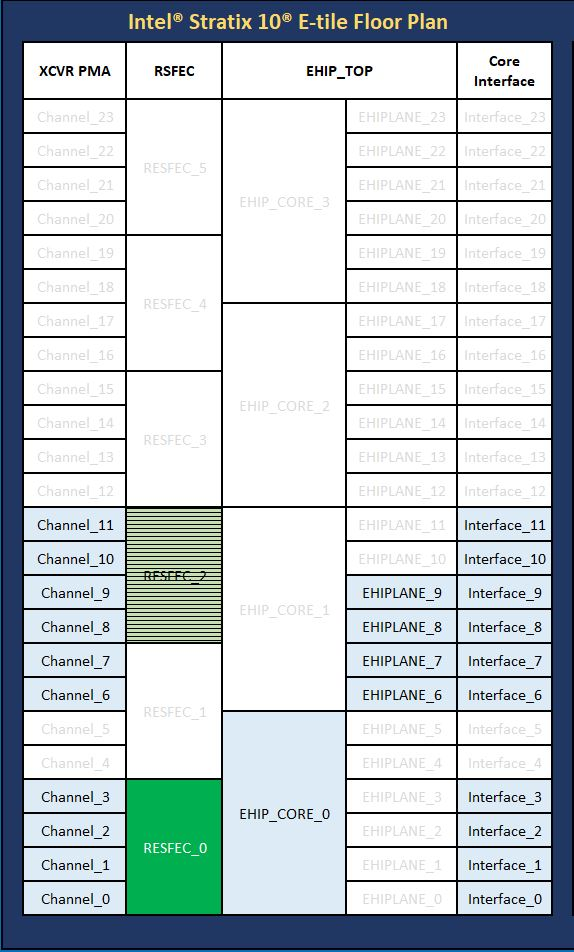

You can configure RS-FEC blocks in many possible combinations depending on your application requirements.

| Channels | FEC Block Mode | FEC Receives Data From |

|---|---|---|

| 0 to 3 | Aggregate | EHIP_CORE |

| 4 to 5 | Bypass | N/A |

| 6 to 7 | Bypass | EHIP_LANE |

| 8 to 9 | Fractured | EHIP_LANE |

| 10 to 11 | Fractured | FPGA core |

Refer to the E-Tile Channel Placement Tool for details about possible channel placement based on system requirements.