2.2.9. Deskew Logic

TX Deskew Logic

Once bonding is enabled (or, in PMA direct high data rate mode, even if bonding is not enabled) deskew logic in the transceiver interface is engaged, which aligns the data that is transferred across multiple channels within the same clock cycle. However, deskew logic requires action on your part. Bit 33 of the TX parallel data, data[33], is mapped to function as the deskew pulse. For PMA Direct high data rate, you must drive the deskew pulse bit of all bonded channels with a pulse that is active on every eighth parallel clock cycle. The deskew logic uses the deskew pulse to align the FIFO. It takes several cycles for the channels to be aligned. You must perform an Avalon® memory-mapped interface read to the TX deskew status register cfg_tx_deskew_sts of all bonded lanes to find out if deskew completed successfully which indicates that all bonded channels have aligned parallel data. The deskew status register also provides further information for debugging if deskew is not successful.

- 0 = not aligned or not enabled or did not receive a deskew bit

- 1 = aligned

- 00 = not yet received a deskew bit

- 01 = not aligned

- 10 = received one set of aligned deskew bits

- 11 = received 16 sets of aligned deskew bits

The deskew mechanism runs continuously. In other words, if the alignment lock is lost, monitoring cfg_tx_deskew_sts informs you about the status. The deskew mechanism works the same way for PMA direct high data rate PAM4 mode for two EMIB channels. In other words, you must send deskew pulses for the data you sent to two EMIBs and at the master PMA interface you are aligned to before sending to a single PMA. In double width mode, the deskew pulse needs to be sent every fourth half clock cycle.

For the extra data bit's detailed usage, contact My Intel support.

| E-Tile Native PHY IP Mode | TX/RX PMA Interface Width | Enable TX/RX Double Width Transfer | Valid Parallel Data | Deskew Bits | Pulse Clock Cycle |

|---|---|---|---|---|---|

| PMA Direct | 16 | No | Data [15:0] | Data[33] | 8th cycle |

| PMA Direct | 20 | No | Data[19:0] | Data[33] | 8th cycle |

| PMA Direct | 32 | No | Data[31:0] | Data[33] | 8th cycle |

| PMA Direct | 40 | No | Data[39:0] | Not supported | Not supported |

| PMA Direct | 16 | Yes | Data[55:40] Data[15:0] |

Data[33] | 4th cycle |

| PMA Direct | 20 | Yes | Data[59:40] Data[19:0] |

Data[33] | 4th cycle |

| PMA Direct | 32 | Yes | Data[71:40] Data [31:0] |

Data[33] | 4th cycle |

| PMA direct high data rate PAM4 | 64 | No | Data[111:80] Data[31:0] |

Data[33] Data[113] |

8th cycle |

| PMA direct high data rate PAM4 | 64 | Yes | Data[151:120] Data[71:40] Data[111:80] Data[31:0] |

Data[33] Data[113] |

4th cycle |

RX Deskew Logic

For PAM4 dual channel mode, the data comes from two EMIBs, so there can be skews in between. To mitigate this, the Native PHY IP implements a deskew function on RX side to align the two EMIBs' data. However, you can only enable this deskew function when the Native PHY IP is configured in PMA direct high data rate PAM4 mode. The deskew logic samples the deskew bit of rx_parallel_data to detect if there is any misalignment. If there is misalignment, the deskew logic calculates skew cycles and outputs the aligned data.

The deskew logic can mitigate a maximum of two skew cycles for single width transfer and a maximum of one skew cycle for double width transfer. When the deskew logic is enabled, there is an added latency of up to three clock cycles even if there is no skew and an added latency of up to five clock cycles if there is two skew cycles.

To observe the misalignment, read the deskew bit in rx_parallel_data[159:0], which is divided into lane 0 (ln0 or rx_parallel_data [79:0]) and lane 1 (ln1 or rx_parallel_data[159:80]).

If it is single data width transfer, the deskew bit is bit [33].

- ln0[33] and ln1[33]

- ln0[33] and ln1[73]

- ln0[73] and ln1[33]

- ln0[73] and ln1[73]

RX Deskew Feature Requirements

- The Native PHY IP must be configured in PMA direct high data rate PAM4 mode.

- The two EMIB channel clocks must be tied together to run on one clock domain.

Figure 40. Two EMIB Channel Clocks Working in the Same Clock Domain

- rx_ready must show that the receiver is ready. If the receiver is not ready, the data is neither reliable nor ready. So you must reset the reset controller until rx_ready indicates that the receiver is ready.

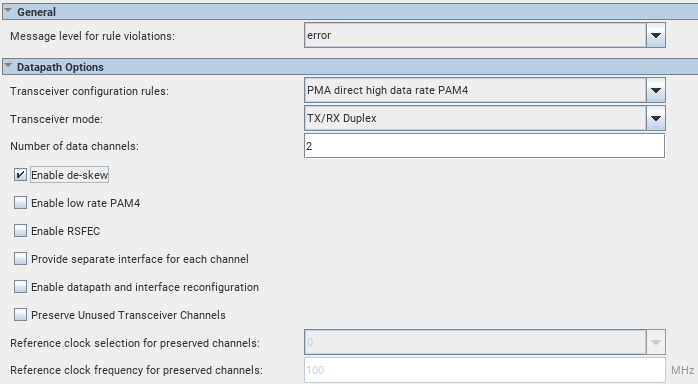

Enabling RX Deskew Logic

- From Native PHY IP GUI, select from Transceiver configuration rules > PMA direct high data rate PAM4.

- Turn on Enable de-skew.

- Because RX deskew logic is applicable for PMA direct high data rate PAM4 only, turn off Enable RSFEC.

- Verify that your data is aligned by confirming that rx_dskw_ready is asserted.